up-to-date electronics for lab and leisure

#### early warning

An alarm c(l)ock for campers

bar code How prices are put in line

choke alarm

Stop pouring petrol out the exhaust

Junior interface

More memory, cassette and printer

routines for the Junior Computer

### Make it for a Song!

### The New Maplin Matinée

Amazing Value For Only £299.95 + £99.50 for cabinet if required.

Easy to build. Latest technology - means less cost. less components and 80% less wiring. Comparable with organs selling for up to £1,000.00. Two 49-note manuals. 13-note pedalboard. All organ voices drawbars. Preset voices: Banjo, Accordion, Harpsichord, Piano, Percussion. Piano sustain Sustain on both manuals, and pedalboard. Electronic rotor, fast and slow. Vibrato and Delayed vibrato. Reverb. Manual and Auto-Wah. Glide (Hawaiian Guitar Sound). Single finger chording plus memory. 30 Rhythms! 8-instrument voicing. Major, Minor and Seventh chords Unique walking bass lines with each rhythm Unique countermelody line with each rhythm. Truly amazing value for money. Full construction details in Electronics & Music Maker magazine.

The complete buyers' guide to electronic components. With over 300 pages, it is a comprehensive quide to electronic possible the comprehensive quide to electronic period produced and page after page of invaluable data. Get a copy now—It the core catalogue you can't albeit to be written.

| Post this coupon now for your copy of our catalogue price £1. Pleaze send me a copy of your 320 page enclose £1. (Plus 25p p6p). If I am not cor satisfied I may return the catalogue to yo money refunded. If you live outside the U or 12 International Reply Coupons. | catalogue. I<br>npletely<br>u and have my |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| I enclose £1.25.                                                                                                                                                                                                                                                         | E5/81                                     |

|                                                                                                                                                                                                                                                                          |                                           |

Name \_\_\_\_\_\_Address\_\_\_\_\_

# MIRPLIN

Maplin Electronic Supplies Ltd. All mail to: P.O. Box 3, Rayleigh, Essex SS6 8LR Telephone: Southend (0702) 554155. Sales (0702) 552911

159-161 King Street, Hammersmith, London W6, Telephone (01) 748 0926. 284 London Road, Westclift-on-Sea, Essex, Telephone Southend (0702) 554000 Both shops Closed Mondays.

| camping clock                                                             | 5-04 |

|---------------------------------------------------------------------------|------|

| Readers may think that this is just a fowl joke, but this electronic cock |      |

| will get you up with the lark, or rather, the sun, in the morning.        |      |

frequency doubler ..... Of the many effects available to the contempory guitarist, the frequency doubler is of particular interest. Unfortunately, it is not the easiest of effects to design due to the fact that the output waveforms of musical instruments bear little resemblance to those in the 'book'.

The addition of the forthcoming interface card will transform the Junior Computer into the complete personal computer system. The card includes additional RAM and EPROM memory and an extra I/O system and will form the essential link between the computer and the outside world.

talk to computers .....

It is taken for granted that pressing a button is enough to do the week's washing. What would it be like if computers 'evolved' yet another stage further and the washing machine could be activated by a mere word?

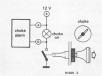

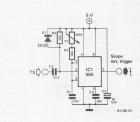

choke alarm ..... 5-20 The main problem with a manual choke is that it is so easily forgotten. The circuit featured in this article is designed to attract the drivers attention to the choke by sounding an audible warning after a preset period of time.

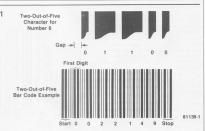

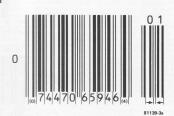

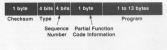

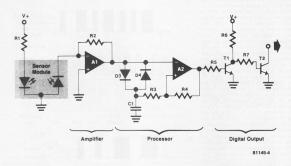

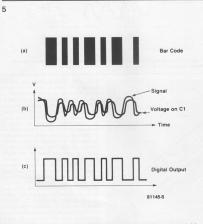

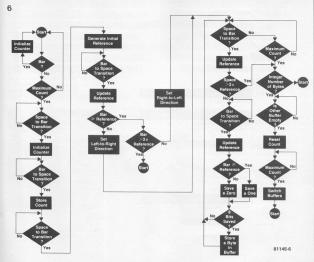

bar codes .....

This article shows that simple bar codes are, surprisingly, not so simple after all.

This, the final article on the logic analyser, puts the theory into practise.

built with non-critical parts at low cost and yet guarantee a highly satisfactory performance.

sophisticated software for the Junior Computer . . . . . . . . . 5-36 This article preveiws two new programs for the Junior Computer, TAPE MANAGEMENT and PRINTER MONITOR.

reading bar codes ...... The electronics behind bar codes,

market ..... 5-50

5-06

5-02

EDITOR: W. van der Horst

UK EDITORIAL STAFF T. Day E. Rogans P. Williams

TECHNICAL EDITORIAL STAFF J. Barendrecht

G.H.K. Dam P. Holmes

F. Kremnelsauer G Nachhar

A. Nachtmann K.S.M. Walraven

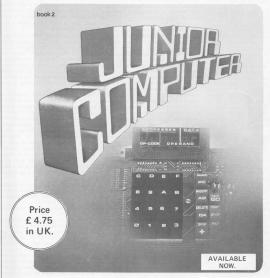

## Book 2 in The Junior Computer Series

#### Junior Computer Book 2

This, the second in the Junior Computer Book series, follows in a logical continuation of book 1 and is an indispensible aid to users of the Junior Computer.

The book contains a detailed appraisal of the software. Three major programming tools, the monitor, an assembler and an editor are discussed in detail together with practical proposals for input output and peripherals. The complete source listing with relevant comments for all described programs, and the entire contents of the EPROM, are included.

#### THE JUNIOR COMPUTER BOOK 2 IS AVAILABLE NOW from

Elektor Publishers, 10 Longport, Canterbury, Kent, CT1 1PE. An order card is enclosed in this issue for your convenience. Price U.K. £ 4.75, overseas £ 4.95 postage and packing inclusive.

#### Radar for the blind

This article is mainly concerned with one technological solution to a severe handicap, total blindness; but to put things in perspective let us first consider the situation of the blind in general.

All higher animals, including man, are extremely mobile creatures. A prerequisite for this mobility is the ability to perceive the environment accurately, and in particular one's immediate surroundings within a radius of, say, 5 metres, In man and most other species, sight is far and away the primary facuity to provide this information. However, there are notable exception

Bats constitute a spectacular anomaly, Most species are virtually blind and yet manage to sense their surroundings in great detail by emitting high frequency sounds (usually above the human choice to the properties of the properties of control of the properties of choice to the properties of properties properti

Blind persons are known to be able to acquire some knowledge of their surroundings by listening to noises around them, such as the sound of voices, footsteps, cane taps, etc. This, however, can only entend their mobility slightly. In the future it may be possible to provide the blind with synthetic vision' by coupling a small relief of the provide to the provide the blind of the provide the blind with synthetic vision' by coupling as mall relief or the provide the blind of the provide the blind of the transport of t

More practical at this time is to utilise the principle of RADAR, which has been in use for more than 40 years (mainly to locate the position of ships and aircraft). When a solution was sought towards developing an aid for the blind, sound waves of ultrasonic frequency, between 20 kHz and 100 kHz, were found to be more suitable than the radio frequency normally employed in RADAR. This is mainly due to the fact that sound waves are propagated at a much lower rate than radio waves, 340 metres per second, as compared to 300 million metres per second. This ultrasonic location method is similar to that used by bats, except, of course, the echoes have to be translated into a frequency that is audible for the human ear.

A highly effective aid using the above principle is known as the 'Sonic Torch'. This was the name given to the first commercially produced device of this kind, manufactured by Ultra Electronics Ltd., An improved version, the 'Radar-

Lantern' has now been developed in Melbourne, Australia.

Weighing less than 350 grams the unit is hand held like a torch, which it strongly resembles as can be seen in figure 1. A beam of ultrasonic energy is radiated from the front of the device and is partly reflected by objects in its path. This is then detected and converted into a sound that the blind person hears in

an ear piece. The sound heard takes the form of a series of 'bleeps', each lasting 0.25 seconds and separated by an interval of silence (about 20 milliseconds). When the 'lantern' is pointed at a hard, flat surface, such as a door, or a window pane a few feet away, the 'bleeps' are heard as clear, pure tones. The pitch of the tones gives a direct indication of the distance between the lantern and the object concerned. By sweeping the instrument's 'light' either vertically or horizontally across an object, the latter's shape may be surmised. The beam is quite directional with a width of about 8 degrees, or 16 degrees in total. By combining the information obtained from scanning the beam with the pitch of the bleeps, the user can obtain a three-dimensional picture of his environment. This may range from very close (about 1 cm.) to 6 metres.

According to the surface that is reflected, the bleeps will vary from 'Chirps' and 'tweets' to 'warbles' and 'swishes', etc., so that with experience the blind person can learn to 'see' every different aspect of his/her environment.

Fred Gissoni, a blind American experienced in the use of the Ultra torch mentioned above, testifies to the effectiveness of this type of aid as follows:

"Once, while demonstrating the use of the aid in a room which was totally unfamiliar to me, I was asked to walk about the room describing objects that I found. I was able to walk about finding clear aisles, chairs and doorways. Suddenly near the centre of the room I

Figure 1, The Radar Lantern. This ultrasonic aid is used by blind people to scan their whereabouts and so form a three-dimensional picture.

found an object which gave a most curious set of signals. Against my better judgement I described the object as giving the impression of being a table but, at the same time, having a fence in the middle of it. This description was greeted with a combination of laughter and applause. The object I was examining was a ping-pong table.

Assume the second of the secon

Gissoni also speaks of how he developed a "memory bank" of characteristic sounds, not necessarily restricted to the sound of the individual "beep"; for instance when standing at the foot of a flight of steps and scanning the beam upwards, the frequency of the signal increases in steps (rather like a musical scale) and this sort of thing is soon memorised.

The best way for a blind person to be trained in using the radarsonic lantern is by being accompanied by someone who can see and so can instruct him/her in the set of 16 illustrated lessons provided each lesson lasts one hour and gradually increases in difficulty. Competence is acquired very quickly, in fact the acquired very quickly, in fact the chairs, open doors and other persons, within the first quarter of an hour. After 10 hours of training, such small objects as an envelope lying on a table can be detected and picked up without any problem.

Thus, after only a few hours of practice the device can be used as a true environment sensor. The four main features of operation are as follows:

Lateral discernment by scanning a narrow beam.

Range of distance information provided by the pitch of the bleep.

Characteristics of the reflected sur-

face are transmitted by varying the timbre of the signal: 'chirps', 'swishes' etc. are heard.

etc, are heard.

4. The intensity of loudness of the signal will gave an idea of the size of the object being scanned and will

of the object being scanned and will vary when the 'point of view' changes (when it is being viewed from the side, for instance). The signal will be at its loudest when the lantern is pointed at right angles to the surface.

As far as the lantern's technical aspects

As all as the lantimer is technical aspects are concerned, the unit is housed in near concerned, the unit is housed in the concerned and the concerned and the concerned and the contained to the concerned and the contained by rechargeable NiCad battery with 150 mA hours capacity. Current drain during operation is mominally 24 mA, so that a fully charged battery will operate for 6 hours. A small battery operate for 6 hours. A small battery

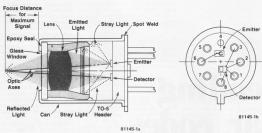

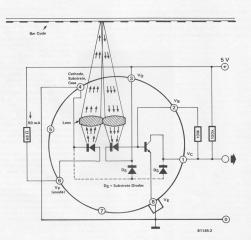

Figure 2. The block diagram of the Radar Lantern

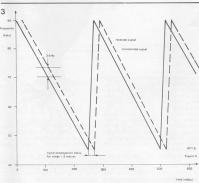

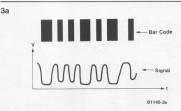

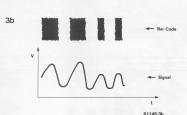

Figure 3. A graph showing the transmitted and received signals.

charger is supplied with the lantern and this will fully charge the battery in 15 hours. Of course, it will 'top up' a partially discharged battery and the charge time should last twice the duration of the period used.

Two ultrasonic transducers (one transmitting and one receiving) are housed in the front of the unit (see figure 1). These are electrostatic types, identical for transmit and receive. They require a D.C. bias voltage of 150 volts which is supplied by a six stage amolifier (see figure 2).

The electronic components include 11 bipolar transistors, 1 field effect transistor and 2 integrated circuit. These are associated resistors, capacitors etc. are mounted on two printed circuit boards contained within the rectangular

portion of the case (see figure 1). The battery is housed to the rear of the P.C. boards.

Only two controls are required – an

ON/OFF switch on top of the unit and a sound volume control on the right hand side. On the left hand side of the case there are two sockets, one for the earpiece and one for the battery charger so that the battery may be charged in situ. A wrist strap prevents the lantern from being accidently dropped.

The unit is basically a frequency-modulated RADAR set and the principle of operation may be explained with reference to the block diagram in figure 2 and the graph in figure 3. The sweep oscillator produces a sawtooth sweep voltage with a rise-time of 250 ms and a flyback time of 20 ms. This voltage

frequency-modulates the ultrasonic oscillator causing its frequency to sweep down from 90 kHz to 45 kHz (and then return) as shown by the full line in figure 3. The ultrasonic oscillator is simply a two-stage multivibrator with "constant current" stages supplying timing currents. These "constant current" stages are controlled by the output of the sweep generator.

The dotted line in figure 3 shows the frequency of the echo signal when it is reflected from an object (a wall, for instance) 3 metres from the lantern. It will be seen that during the 250 millisecond duration of the sweep there is a frequency difference of 3 kHz between the transmitted and reflected signals. The echo signal is detected by the receive transducer, amplified and fed to the mixer (which makes use of an MPF104 FET). Since the transmitted signal is also fed to the mixer (see figure 2) the 3 kHz differential frequency will appear at the mixer output. This signal, which is in the audio range, is boosted by the audio amplifier and fed to the earpiece, thereby producing characteristic bleep described above.

Cheardters to believe used to be above or consequence of costs, it becomes apparent that a variation in the reflecting objects of distance wow the consequence of the cost of

confusion" of the real world, full of objects both stationary and moving and of varying shapes and textures, the blind person's ears assailed by a very complex intermodulation of audio signilia and the total signal heard could well be a far cry from the pure tone situation as illustrated in figure 3. Notwithstanding the difficulty of analysing the heart of the country of the cou

The 'lantern' contains good quality components with a 0° to 70° temperature rating and the battery is designed to operate between 0 and 50°. The instrument might therefore fail to operate in sub-zero temperatures. It is however suitable in rainy conditions, although it should not be totally immersed in water.

It may be concluded that the sonic torch device offers an effective solution towards increasing the mobility and general emancipation of the blind.

With thanks to Mr. Y. W. Park and to

the 'Radar for the Blind' Club, Preston (Victoria), Australia.

# camping c(l)ock

Why does a camper put up his tent in the middle of lush countryside rather than Piccadilly Circus, if not with the get a little closer to the birds and the trees? What could therefore be more appropriate than to wake up at the crack of dawn to brilliant sunshine thanks to the cheerful sound of this man-made feather-brain? For it is the son that makes it sing its dawn chorus. This property of the country of the country of the country of the crack of the country of the

Attentive readers will now point out:

"Yes, but what happens when it

rains?!" Well, then there's nothing to

get up for, is there?" Might as well stay

in bedl And so our understanding

feathered friend won't make a sound

until the village pub opens. Unfortunately, however, the real dawn chorus

won't be nearly as considerate, come

rain or 'shine, meaning you will have to

resort to cotton wool, or, if the worst

comes to the worst, to the shot-gun.

Now that we've fully woken up to the

idea, let us take a look at the circuit

diagram of this ingenious device. This is

shown in figure 1.

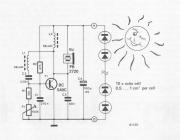

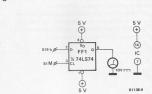

As you can see, this is a straightforward affair, a bit of a lark really. All it contains are a few miniscule solar cells and a buzzer. From the electronic point of view the device has nothing to be cocky about, but the main thing is, it works and it is fun to build.

A fairly conventional oscillator is constructed around T1. It is unique in that it operates from an extremely low supply voltage (0.5 V!) and provides a clearly audible alarm signal on very little current. The signal is produced by

the buzzer, type PB 2720 from Toko. This is loud enough to get through to even the soundest sleepers, provided, of course, the gadget is placed in close proximity.

The camping c(I)ock's lifeline is its power supply. Ten tiny solar cells are connected in series to make sure operation is not 'half cock', even when it's pouring outside. Each has a surface area of about 1 cm2. The types used in our prototype c(l)ock were 6 x 19 mm in size and capable of delivering 20 mA of short-circuit current. If readers are unable to obtain this particular type, any other will do, as long as the total surface area remains the same. In other words, the oscillator will work equally well, whether the 0.5 V supply is provided by two 5 cm2 cells or by ten 1 cm2 ones. If less sensitivity is required, the surface area may even be smaller than 10 cm2.

The voltage divider used to preset T1 has been made variable, so that the amount of sunlight required to activate the oscillator can be preset with P1. The sensitivity has a very wide range: when P1 is set at a minimum resistance, quite a lot of sunlight is needed for the buzzer to sound; when P1 is set at a maximum level, the glow of a burning match be enough to cause the cock to

Readers may think this is a

'cock-and-bull' story, as this

crow. It failed its oral at the

electronic cock does not actually

crowing school, sounding more

like a chirping cricket and you

either, for, after all, it does look

like the farm-yard fowl - quite a

may think 'that's not cricket'

handsome specimen, in fact,

Nevertheless, it fulfils its task

admirably and will get you up

with the lark, or rather, the sun.

Figure 1. Considering the alarm c(I)ock is fully automatic and even compensates for bad weather, the circuit diagram is surprisingly straightforward.

2

Miscellaneous: L1,L2 = 56 mH coil B2 = Toko PB 2720 buzzer Ambit

#### A few practical points

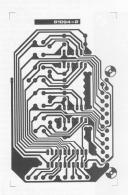

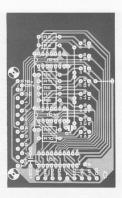

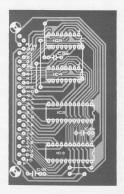

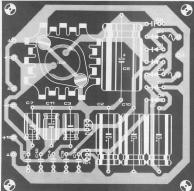

Although the circuit is so straightforward that most people can probably manage to build it without a printed circuit board, our designers decided to create one anyway. The component overlay is shown in figure 2. Two holes have been drilled at equal distance from each other and from the ones belonging to the recommended Toko buzzer, thus this can easily be mounted on the board.

As far as the housing is concerned, there are various alternatives. A tiny case may be used and the solar cells can be mounted on the outside. A better solution is to insert the cells inside a transparent plastic case. It would be more practical, however, to separate the solar cells from the rest of the circuit by placing them in a waterproof perspex case with a very long cable connected to it. The solar cell case is then put outside the tent and the buzzer section is kept inside.

Of course, artistically inclined enthusiasts might like to try their hand at copying the prototype model shown on the cover of this issue.

By the way, an on/off switch is not necessary for once. When you get fed-up of hearing the cock crow, just throw a cloth over it - that'll shut him up!

Figure 2. The camping c(I)ock printed circuit board. Construction should only take about ten minutes.

#### Parts list: Resistors: R1 = 10 k R2 = 47 k P1 = 100 k preset Capacitors: C1 = 270 n C2 = 220 n C3 = 68 n C4 = 100 µ/6 V Semiconductors: T1 = BC 549C solar cells: see text

Many types of effects units are available to the contempory guitarist and their use is considered the norm rather than the exception in the music of today. Of these effects, the frequency doubler is of particular interest and is fast gaining popularity with the resourceful quitarist.

The basic idea of frequency doubling is essentially a good one since the resultant effect can be very desirable to the progressive musician.

By far the most commonly used method of frequency doubling is full wave rectification. This principle is relatively simple, but suffers from the flowshock that it will only work effectively with perfectly simusoidal waveforms, and then only to a certain degree. Unfortune of the common suffers of the common

us the sine and cosine components of the formula.

Before the signals can be mixed, the amplitude of one of them will have to be made constant, as otherwise the to be made constant, as otherwise the output signal of the mixer would not vary with the input signal, but would change quadratically. For this reason one of the signals is passed through a control amplifier to ensure that its fact called automatic gain control, or AGC for short.

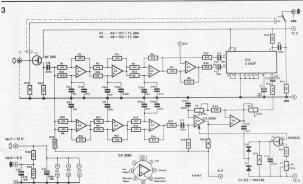

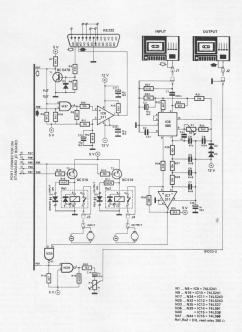

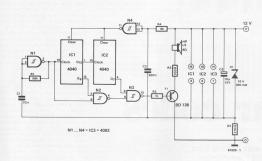

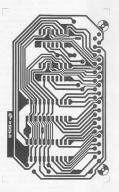

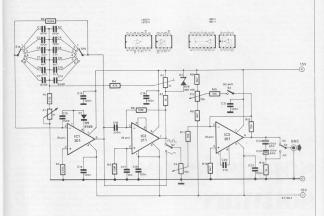

#### Circuit diagram

Figure 3 shows how the above ideas can be put into practice. A source

# frequency doubler

Unfortunately, a good frequency doubler is not the easiest of effects units to design. This is due to the fact that the output waveforms of musical instruments bear little (or no) resemblance to those in 'the book'. In consequence, the practical result rarely conforms to the theory. The design presented here however gives a reasonable account of itself especially when cost is taken into consideration.

as the input signal waveform approaches that of a squarewave.

It all works very well in theory, but the

It all works very well in theory, but the end results, when used with a musical instrument such as an electric guitar for instance, can be very far from satisfying to say the least! What is more, a great deal of care and attention has to be paid to the unwanted DC output component. This is of course easier said than done. Clearly, full wave rectification is a non-starter, so what other method can be used? As the frequency doubler has to be used with a guitar, a circuit was required which was capable of doubling the frequency throughout the middle range of the audio spectrum effectively. without distortion and, if possible, without any side effects. After much discussion a possible solution came to

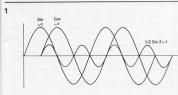

sin ω t · cos ω t = ½ sin 2 ω t

In simple terms, this formula states that the product of a sine and a cosine waveform of the same frequency, is a signal of twice the frequency, is a signal of twice the frequency, it could be assumed that this will only hold be assumed that this will only hold be assumed that this very signal can be looked upon as being made up from a (large) number of sinewaves and, therefore, the above statement will remain true.

This can be proved not only by means of formulae, but also in the form of the graph shown in figure 1. This principle would appear to be an ideal basis for our frequency doubler.

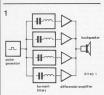

#### Block diagram

A simplified block diagram of the frequency doubler is shown in figure 2 to illustrate the principle of the circuit. Basically, two signals of the same frequency but which are 90° out of phase with each other, are fed to a (bipolar) mixer. Two waveforms are therefore derived from the input signal; the original waveform and the same signal with a phase shift of 90°. This gives

follower (T1) is used as an input stage in order to obtain a high input impedance. Once the signal has been split, it is phase shifted by means of two active filters constructed around a series of opamps. One signal is filtered by components and the other by opamps A5... A7. Opamp A4 is used to give a further 180° phase shift for the first signal so that the mixer can be controlled symmetrically.

The two signals are in fact multiplied by IC3, which is the SO42P double balance mixer, ideal for this particular application. A signal of twice the frequency of the input signals can be obtained from the output (pin 3) of this IC. Switch SI has been included so that the frequency doubler can be switched in or out of the circuit as required.

The only thing that remains to be mentioned is the AGC system. The main component in this section of the circuit is an operational transconductance amplifier (OTA). In the circuit diagram this is shown as IGA. The gain of an OTA can be varied by means of a control current at pin 5 of the IC, the larger this current, the higher the gain, AGC and the AGC action that the AGC section the FET T2) completes the AGC section.

Operation is simple: The output signal from A8 is rectified by D1 and D2. Thus, a smoothed DC signal appears at the gate of the FET (T2). The higher this DC level, the lower the voltage across R21 and the less T2 will conduct (lower drain current). Since the drain of the FET is connected to the current of the FET will be controlled and the thin the training of the OTA will be controlled and the other of the other ot

achieved by incorporating the network R33, P3 and C15 between the output

Figure 1. Sin  $\omega$  t.cos  $\omega$  t = ½ sin 2  $\omega$  t. The product of a sine and cosine signal of the same frequency produces a resultant signal of twice that frequency (albeit at half the amplitude).

Figure 2. The block diagram of the frequency doubler. The principle shown in figure 1 can be put into effect by splitting the input signal into two and altering their phase relationship until they are 90° out of phase with each other and then mixing them.

of A8 and the inverting input of the OTA, This means that the lowest peak of the OTA can be shifted. As a result, the effect of the frequency doubler may be varied by P3 with respect to the lower frequency end of the range depending on the characteristics of the particular OTA used. This adjustment is best carried out by ear. Potentiometer P1 is used to adjust the control current of the OTA to ensure the correct operation of the AGC section. This will be when a quiescent current of 20 µA is measured between the drain of the FET and pin 5 of the OTA (with no input signal present). This corresponds to a voltage of 940 mV across R17. Finally, potentiometer P2 enables the amplitude of the signal 'processed' by the AGC section to be present. This potentiometer will be positioned correctly when no difference in output level is detected between the original signal and the frequency doubled signal.

#### Results

The protorype of the frequency doubler was found to live up to its expectations reasonably well. Its frequency range was found to be between 300 and 3500 Hz and therefore well within the spectrum produced by a guitar.

Applications for the frequency doubler need not be confined to guitar only. Enterprising misicians will no doubt be inspired to dream up all sorts of other possibilities as well. For example, tests showed that speech signals could all be doubled in frequency fairly well, although, to be honest, the audible result was far from musical!

The SO42P is available from Electro-

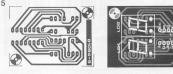

Figure 3. The circuit diagram of the frequency doubler. Briefly, opamps A1...A7 provide the phase shift, IC4, A8, D1, D2 and T2 form the AGC section and IC3 performs the actual mixing.

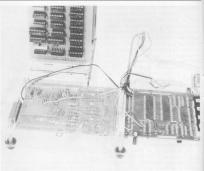

Now that the interface card is to be added to the Junior, the computer will be 'fully grown', that is, it will have all the hardware it requires. Its 'Torain', the software, may however be further expanded. It is time for the computer to 'talk like an adult', or rather, operate in a higher level programming language and it would of course be interesting for the operator to lawn to work with such a machine language. Elsewhere in this issue machine language and didditional system

ible, the sky is the limit as far as the theoretical expansion possibilities are concerned, the final result being a computer with multiple facilities.

A single board system, on the other hand, incorporates everything on a single card, It all depends on what the 'everything' must comprise to suit the user's purposes (and therefore on the size of the card). Putting 'everything on a single card' is a bit of a gamble: you either win or you lose. It means the user

# the fully fledged Junior Computer

#### On board data busing provides for wider communication

Since Junior Computer Book 2 is now available, it is time we moved on to the next and final stage in the Junior Computer project. The addition of the forthcoming interface card will transform the Junior into the complete personal computer system. This card will from the essential link between the computer and the outside world as it includes additional RAM and EPROM memory and an extra I/O system. It also enables further memory cards and a cassette recorder to be connected to its buffered bus allowing the Junior Computer to communicate with the operator (and vice versa) in a far more sophisticated

This article is the first in a series of three and propose to describe the theoretical and practical aspects of the hardware extension. These articles will form the basis of Books 3 and 4, to be published later this year, and may therefore be lacking in fine detail (due to lack of space) but the intention is to give our readers a good idea of what is in store.

software lincluding two software 'sids') are described in detail, but the language are described in detail, but the language are described in detail solves the language of langua

In any case, Elektor is planning to provide a 16K dynamic RAM card within the near future. This would constitute an economical alternative to two RAM/EPROM cards which both include 8K of RAM.

First things first, what extensions are required to bring the Junior Computer to adulthood?

To bus or not to bus . . .

Computer systems especially designed for hobbytist are available in two types: bus systems or single board systems. The former employs several cards (printed circuit boards) to incorporate the components. The cards are all the components. The cards are all the 100 x 160 mm, for instance) and are individually linked by means of a bust. This is a printed circuit network in which equally positioned points (such as connector pins) are interconnected, since the system is universally compatible.

has to estimate his/her needs very carefully from the start and this often proves to be quite a handicap, as it is difficult to plan ahead when the possibilities are largely unknown.

Single board computers are mainly used to teach operators and as part of relatively straightforward process control systems (where the computer is switched on permanently). In its standard version the Junior Computer is in fact a single board system, being designed to teach beginners. The standard version is already being used by many for all sorts of applications already, ranging from A/D conversion to process control in the manufacture of semiconductors, Thus, the interface is a purely optional addition and the expansion connector may be left untouched.

Nevertheless the expansion connector is there and for two very good reasons; it allows a cassette recorder to be connected as a backup memory (to boost a RAMshackle memory), thereby permitting full use of the total 64K memory capacity and second, it are not seen to be connected as the connected equipment in but connected distinct and the connected and

Once the expansion connector is employed, the Junior Computer is no longer a single board system. This does not mean its possibilities as a bus system will be infinite. On the contrary, the computer is limited by its own hardware.

In any case, the expanded version bears no physical resemblance to the average basic system. All the extensions mentioned above are included on the interface card, which has the same size as the main board, so that they can be 'sandwiched' together. An existing SC/MP bus card may be linked to the interface card to house several other memory cards

In spite of the bus card addition, therefore, the Junior Computer is not a bus system, but rather a 'double-decker' sandwich! However, never mind what category the computer could fall into let's look at the system itself.

#### The interface card

The word 'interface' means 'link', Here the interface card provides the Junior Computer with a vital link with the outside world in the form of various communication channels: additional I/O. a cassette interface, an RS-232-interface and an internal connection with the buffered bus board.

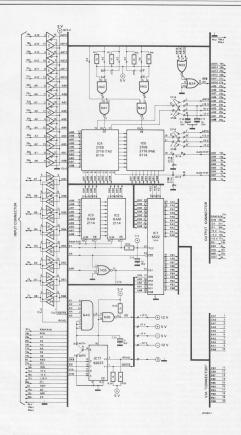

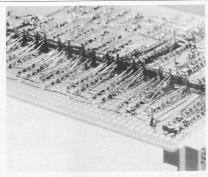

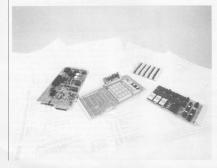

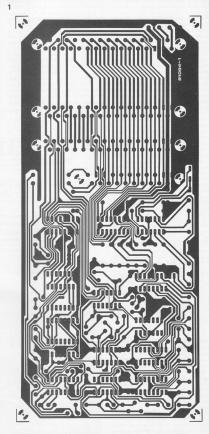

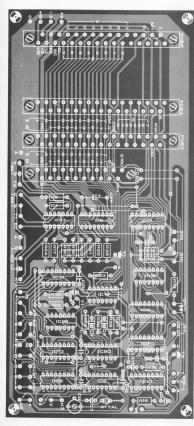

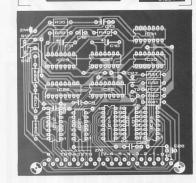

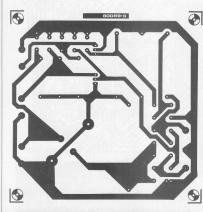

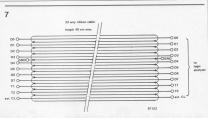

All the electronics involved may be found in figures 1 and 2. As can be seen, it is more elaborate than the main board, even though it is equally compact in size. Each component will now be discussed separately.

#### The buffers: softening electronic blows

All the connections belonging to the INPUT CONNECTOR are shown to the left of figure 1. This connector together with five links to the port connector (see figure 2) allow for data transfer to and from the standard Junior Computer. With the exception of lines EX and K1 . . . 6, which serve the interface card only, all the lines lead to the OUTPUT CONNECTOR on the right-hand side of figure 1. This connects the interface to the bus board which in turn permits one or more memory cards to be connected. The well-known A address lines are marked AB here and the D data lines are shown as DB; the B stands for 'buffered', Why is buffering necessary? Well, for two reasons, First, it prevents an overload condition brought about by too many connections, Second, it enables data transfer along the data lines between the standard Junior Computer and the interface and memory cards to be controlled. N1 . . . N16 act as address buffers. Since

addressing always takes place by way of the 6502 on the main board, the triangles are pointing in the direction as indicated: left for inputs, right for outputs. N17...N32 act as data buffers and here the even number buffer inputs point to the right and the outputs to the left, whereas the odd buffer inputs point to the left and the outputs to the right.

Three situations are feasible:

1) Ports N17...N32 with odd numbers are active and the even ones

are inactive when both WRITE and READ are logic 0. Data may then flow from the standard board to the extensions, if data is to be written either in the interface memory, the extension memory (bus memory) or in the I/O. 2) When WRITE and READ are both

logic 1, ports with odd numbers between N17...N32 are inactive (tri-state, that is to say, high impedance at both the inputs and the outputs) and the even ones are active. Data may then flow from the extension boards to the main board, if data is to be read either from the interface memory, the bus memory or from the I/O. 3) All ports between N17 and N32 are

inactive when WRITE is logic 1 and READ is logic 0. No data will be transferred. This happens whenever data is being read or written inside the standard Junior memory or in the I/O. The WRITE and READ signals are generated by the PROM IC17. More about this later.

N.B. A fourth theoretical possibility is that WRITE = logic 0 and READ = logic

1, all ports in the N17...N32 range being active at the same time. This should never happen,

#### Additional I/O

The VIA IC1, type 6522, merits individual attention. As a matter of fact, a whole chapter will be devoted to the subject in the second half of Book 3, The VIA (Versatile Interface Adapter) is remarkable in that it offers more facilities than the standard I/O nucleus the 6532 PIA. As shown in figure 1, the VIA 'CONNECTOR' incorporates the

relevant connections with the outside world. (It is put in inverted commas, as it is not a real connector). The 6522 is controlled by address lines ABØ ... AB3 and by various signals produced by the control bus.

The eight data lines and the IRQ output signal (interrupt after a timer time out) will be familiar from Book 1.

Like the 6532, the 6522 features two chip select signals. Its CS2 is connected to the output signal K6 of the address decoder IC6 on the Junior Computer's main board. The CS1 signal is linked to the output of N35 which is controlled by K6 and AB9. For the VIA to be activated CS2 and CS1 will have to be Ø and 1 respectively. N35 will now act as a NOR gate, its output being logic 1 when both inputs AB9 and K6 are logic zero (in the case of the 6532, A9 has to be logic 1). Since A8 (AB8) is not connected to either the 6522 or the 6532, the VIA 6522 can be addressed as

follows: 1800 = 1900 . . . 18FF = 19FF (AB8=X:AB9=0:K6=1) and the PIA 6532;

1A00 = 1B00 . . . 1AFF = 1BFF

(A8=X:A9=1:K6=1) Since double addressing is excluded, as

A8=AB8=X, 256 addresses are available for both the PIA and for the VIA. In the former case 19 different memory locations are available for the PIA in addition to 128 bytes of RAM, As can be seen in figure 1, address lines AB4 . . . AB7 are not connected. Thus, there are only 16 different memory locations for the VIA.

#### Interface memory

The interface card has room for up to 5K supplementary memory which is 1

selected by K1 . . . K5. This is enough to allow the main board's decoded addresses (8K) to be fully utilised (including 1K for the PIA plus VIA).

In the first place, additional RAM is now available. Even without using other extension facilities, the operator can already dispose of 1K of RAM on the interface card by way of IC2 and IC3 (1024 data nibbles per IC). The RAM is selected when K1 = CS = logic Ø. Thus, ts address range covers:

0400 ... 07FF.

In other words, four pages (04 . . . 07) are available linking up nicely with the standard RAM pages 00 ... 03, so that engthy user programs can now be stored 'in one piece'

Both IC4 and IC5 may be 1K RAM (8114), 1K EPROM (2708) or 2K EPROM (2716) types. One or two signals K2... K5 select each IC with the aid of the clock signal  $\Phi 2$  (ports N41...N44). The latter is necessary to time the reading and (if appropriate) the writing process.

| K2 = logic 0 → addresses Ø8ØØ   | ØBFF |

|---------------------------------|------|

| K3 = logic 0 → addresses ØCØØ ! | ØFFF |

| K4 = logic 0 → addresses 1000   | 13FF |

| VE = logic 0 -> addresses 1400  | 1755 |

For 1K of RAM (8114) or 1K of EPROM (2708) each IC provides various selection possibilities, For 2K of EPROM (2716) two K signals are combined: K2 & K3 for IC4 (2716) (address range Ø800 . . . ØFFF) and K4 & IC5 for IC5 (2716) (address range 1000 . . . 17FF). Solder pins A . . . F are supplied to select these addresses. They are interconnected to suit the type of IC8. The same is true of pins G...O and G'...O', which are linked according to the value of the supply voltages and also according to whether an

additional address line AB10 or the RAM-R/W signal is required or not.

#### Full address decoding

In the standard Junior Computer only 8K out of a total of 64K is decoded. Address lines A13.. A15 are not used, as a result of which pages ØX, where  $X = \emptyset ... F$ , are also accessed on pages 2X, 4X, 6X, 8X, AX, CX and EX, and pages 1X, where X = Ø . . . F, are also accessed on pages 3X, 5X, 7X, 9X, BX, DX and FX. In this particular situation pin D belonging to the address decoder IC6 on the Junior's main board is grounded via a wire link.

If the memory is to be extended by more than 5K, we will have to set up an address decoding system that enables us to access any address within the

2000 ... 2FFF range.

This is achieved as follows. First pin D of IC6 in the standard Junior Computer is linked to pin EX - move the wire bridge to EX! Pin EX=pin D is connected to the output of inverter N34 which is controlled via the NOR gate N33 and this in turn is connected with AB13 . . . AB15. As soon as one of the three address lines mentioned becomes logic 1, EX and therefore D of IC6 become logic 1 too. As a result, none of the output signals KØ . . . K7 of IC6 will be low, If all three address lines AB13 . . . AB15 are logic zero, pin D of IC6 will also be low (grounded) and one of the KØ...K7 signals will become logic zero. This means the I/O and memory on both the main board and the interface board can only be accessed in pages ØX and 1X, where X=Ø ... F; pages 2X onwards can be accessed via the bus card. Supplementary address decoding is required on either the

RAM/EPROM card or on the 16K dynamic RAM card to select one or more memory areas in the relevant address range 2000 . . . FFFF.

The EX output signal is also sent, under the denomination 8KØ, to an address input of the PROM (IC17). This contains 32 bytes in all, but only two bits in each byte, Y1 (=WRITE) and Y2 (=READ), are used. The two bits control data buffers N17...N32. The 32 bytes can be accessed via the five address lines E...A, which will be

described later on. Seeing as the PROM is so complicated to access, why have one at all? Why not simply make do with the R/W signal in the manner provided on the Junior's main board? To find out, let's see what happens when data is read from the RAM. EPROM or I/O stationed on the main board. If the R/W signal is directly connected to READ and WRITE signals on the extension card, the eight data buffers with inputs facing the interface card will be enabled. These inputs will in fact not be connected to anything at all - in other words they will be left hanging in mid-air - as the interface card is not being addressed! Thus, the inputs will be in a random logic state and, as their outputs are activated, the information that appears on the data lines is bound to be incorrect. The solution is therefore to control the data bus buffers with the address system of each circuit. In the example given above (reading data into one of the ICs on the main board) the CPU 6502 does not require anything beyond the buffers and so these must be disabled. It should be noted, however, that such problems do not arise when data is being written on the main board.

The PROM is included for another reason as well, The NMI, RES and IRQ vectors can now (once the address decoding is complete) be stored at their true addresses FFFA . . . FFFF, instead of 1FFA ... 1FFF (in the standard EPROM). This will only work, of course, if page FF is really stored in EPROM memory. Since page FF is included on a RAM/EPROM card here that is connected to the computer by means of a bus board, we will refer to it as bus board memory fron now on.

N.B.: As soon as a bus board is used to connect a memory card, page FF must be included on EPROM with the correct vectors, so that 'double crossing' addressing (where FF=1F, etc.) is no longer possible.

Now to get back to addressing the PROM IC17. The five address signals with which the WRITE and READ signals are obtained are as follows:

A, The R/W or R/W signal (the dash above the W merely means: 'enabled when logic zero' and helps avoid confusion).

B. The 'VIA' signal. This is obtained from N35's output and is none other than the CS1 signal inherent to the

VIA IC1. Inside the 1K zone decoded by K6=logic zero, the PIA is situated above the data buffers and the VIA below them.

C. The  $\overline{\text{KX}}$  signal. This is derived from N36 which is enabled by the output of N40. This is logic zero when one of the K1...K5 lines is logic zero, in other words, when the interface

memory is being accessed.

D. The 8KG signal. This is another name for the EX signal which was mentioned earlier and will be logic zero when the first 8K (of memory and I/O on both the main and interface board) is being addressed and will be logic 1 whish

bus board memory is being addressed. E. Pin E of ICTJ is either Inked up with 45 V (wire link RS) or grounded (wire link RT). Pin E must be logic zero when no bus board memory is consected (indicated as WITH, meaning WITHOUT) and must be logic 1, when it is in fact connected (WITH, meaning WITHOUT). The wire link is RS or RT is necessary for the simple reason that it is necessary for the simple reason that it was board memory; is to be connected or not.

Writing or reading memory on the interface card (IC2...IC5). Eight data buffers are enabled to indicate either read or write in PROM addresses 00 and 01

Reading EPROM and either reading or writing RAM or PIA on the main board. The data buffers are all disabled (PROM addresses Ø4 and Ø5).

Reading or writing into the VIA.

Since this involves the interface card

| PROM-address (hex) | E = WITH of WITH | D = 8K® | C = KX | B = VIA | A = R/W | Α8 | ۲۸ | Уб  | YS | Y4 | ۲3 | Y2 = READ | Y1 = WRITE | PROM-data (hex) |

|--------------------|------------------|---------|--------|---------|---------|----|----|-----|----|----|----|-----------|------------|-----------------|

| 00                 | 0                | 0       | 0      | 0       | 0       | 0  | 0  | 0   | 0  | 0  | 0  | 0         | 0          | 00              |

| 01                 | 0                | Ø       | 0      | 0       | 1       | 0  | 0  | 0   | 0  | 0  | 0  | 1         | 1          | 03              |

| 02                 | 0                | 0       | 0      | 1       | 0       | 0  | 0  | 0   | 0  | 0  | 0  | Ø         | 0          | 00              |

| 03                 | 0                | 0       | 0      | 1       | 1       | 0  | 0  | 0   | 0  | 0  | 0  | 0         | 0          | 00              |

| 04                 | 0                | 0       | 1      | 0       | 0       | 0  | 0  | 0   | 0  | 0  | 0  | 0         | 1          | 01              |

| 05                 | 0                | 0       | 1      | 0       | 1       | 0  | 0  | 0   | 0  | 0  | 0  | 0         | 1          | 01              |

| 06                 | 0                | 0       | 1      | 1       | 0       | 0  | 0  | 0   | 0  | 0  | 0  | 0         | 0          | 00              |

| 07                 | 0                | Ø       | 1      | 1       | 1       | 0  | 0  | 0   | 0  | 0  | 0  | 1         | 1          | 03              |

| 08                 | 0                | 1       | 0      | 0       | 0       | 0  | 0  | 0   | 0  | 0  | 0  | Ø         | 0          | 00              |

| 09                 | 0                | 1       | 0      | 0       | 1       | 0  | 0  | 0   | 0  | 0  | 0  | 0         | 0          | 00              |

| ØA                 | 0                | 1       | 0      | 1       | 0       | 0  | 0  | 0   | 0  | 0  | 0  | 0         | 0          | 00              |

| ØB                 | 0                | 1       | 0      | 1       | 1       | 0  | 0  | 0   | 0  | 0  | 0  | 0         | 0          | 00              |

| ØC                 | 0                | 1       | 1      | 0       | 0       | 0  | 0  | . 0 | 0  | 0  | 0  | 0         | 1          | 01              |

| ØD                 | 0                | 1       | 1      | 0       | 1       | 0  | 0  | 0   | 0  | 0  | 0  | 0         | 1          | 01              |

| ØE                 | 0                | 1       | 1      | 1       | 0       | 0  | 0  | 0   | 0  | 0  | 0  | 0         | 0          | 00              |

| ØF                 | 0                | 1       | 1      | 1       | 1       | 0  | 0  | 0   | 0  | 0  | 0  | 0         | 0          | 00              |

| 10                 | 1                | 0       | 0      | 0       | 0       | 0  | 0  | 0   | 0  | 0  | 0  | 0         | 0          | 00              |

| 11                 | 1                | 0       | 0      | 0       | 1       | 0  | 0  | 0   | 0  | 0  | 0  | 1         | 1          | 03              |

| 12                 | 1                | 0       | 0      | 1       | 0       | 0  | 0  | 0   | Ø  | 0  | 0  | 0         | 0          | 00              |

| 13                 | 1                | 0       | 0      | 1       | 1       | 0  | 0  | 0   | 0  | 0  | 0  | 0         | 0          | 00              |

| 14                 | 1                | 0       | 1      | 0       | 0       | 0  | 0  | 0   | 0  | 0  | 0  | 0         | 1          | 01              |

| 15                 | 1                | 0       | 1      | 0       | 1       | 0  | 0  | 0   | Ø  | 0  | 0  | 0         | 1          | 01              |

| 16                 | 1                | 0       | 1      | 1       | 0       | 0  | 0  | 0   | 0  | 0  | 0  | 0         | 0          | 00              |

| 17                 | 1                | 0       | - 1    | 1       | 1       | 0  | 0  | 0   | 0  | 0  | 0  | 1         | 1          | 03              |

| 18                 | 1                | 1       | 0      | 0       | 0       | 0  | 0  | 0   | 0  | 0  | 0  | 0         | 0          | 00              |

| 19                 | 1                | 1       | Ø      | 0       | 1       | Ø  | 0  | 0   | 0  | 0  | 0  | 0         | Ø          | 00              |

| 1A                 | 1                | 1       | 0      | 1       | 0       | Ø  | 0  | 0   | 0  | 0  | 0  | 0         | 0          | 00              |

| 1B                 | 1                | 1       | 0      | 1       | 1       | Ø  | 0  | 0   | 0  | 0  | 0  | 0         | 0          | 00              |

| 1C                 | 1                | 1       | 1      | 0       | 0       | Ø  | 0  | Ø   | 0  | 0  | 0  | 0         | 0          | 00              |

0 0

0 0 0

0 0

0

eight data buffers will be enabled to indicate either process (PROM addresses 06 and 07).

03

0 0 00

4. Writing or reading bus board memory (PROM addresses &C and ØD). Since once again E is low (WITH=WITHOUT), no bus board memory is connected and so the data buffers must all be disabled. The NMI, RES and IRQ vectors are automatically defined by the standard EPROM of the Junior Computer.

- 5. See point 1 (PROM addresses 10 and

- 11). 6. See point 2 (PROM addresses 14 and

- 15).

- 7. See point 3 (PROM addresses 16 and

- 8. This partly corresponds to point 4 (PROM addresses IC and 1D). As in cases 5...7, E is logic 1 (WITHE WITHOUT) which means the bus board memory must be connected. Now however the data buffers will have to be enabled to allow data transfer to take place in one direction or another. The

three vectors are now sought in page FF. This must be connected to the EPROM which specifies the three vectors at addresses FFFA...FFFF.

It can be concluded that half of the 32 bytes inside the PROM IC17 are truly necessary. The other 16 logic states are irrelevant, since such combinations as D=8K6\_C=KX and B=VIA. Upst do not arise. In the other 16 cases however Y1 and Y2 are always low. This indicates that the data buffers are prepared for a write operation and so perfectly harmless.

That covers figure 1, now for figure 2..

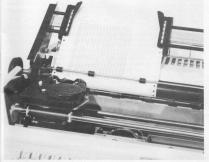

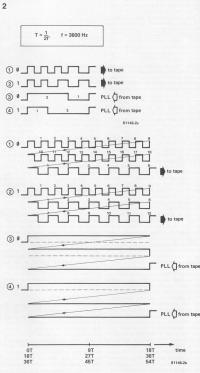

#### The cassette interface

Most of the components shown in figure 2 refer to the cassette interface. This includes everything that is needed in the way of hardware (the software involved is dealt with elsewhere in this issue) to transfer data to and from a cassette recorder. When data is being a read it is the tape that is emitting loallying back) data and when it is being written into the cassette it is recorded on tape.

The data is transferred to and from the

6502 uP by way of port line PB7 belonging to the port connector, When data is being written during the DUMP/ DUMPT subroutine of the TAPE MANAGEMENT system program, PB7 functions as an output and so do PB5 and PB6. Post PB5 will then be low and PB6 high. As a result, the input of N38 with pin number 8 will also be low and so its output will be high (N38 has an open collector output which is high ohmed whenever it is logic 1). Since PB5 is logic Ø the PNP darlington T3 is connected up via R15 and so the red LED D5 (OUTPUT ON) lights and relay Re2 is activated. The two contacts of output J4 are interconnected. If these are connected in series with the motor of the recorder OUTPUT (remote control), the recorder can be switched on by means of software, provided that the recorder is ready to record.

Since P86 is logic 1 during a write operation, T2 will not conduct, the green LED D4 will not light and relay Re1 will not be activated. The output of N39 leads to P2 via R20 and C14 and P2 presets the maximum recording level. J2 is the data output.

When data is read on tape during the subroutine RDTAPE in TAPE MANAGEMENT, PB7 acts as an input and PB5 and PB6 will again be outputs. Port PB5 is logic 1 now and PB6 logic 0. As a result, N38 can pass on the output signal of IC7 to PB7 after inverting it. Pbrt 39 remains connected through, so that signals also reach the data output 12, but without doing any hard to ding any large.

Now that PB5 is logic 1, the red LED D5 will not light. PB6 will now be low causing T2 to conduct, the green LED

D4 (INPUT ON) to light, relay Re1 to be activated and the contacts of J3 (remote control for the playback recorder INPUT) to be disconnected. There is no absolute need to use

separate recorders for storing and fetching data. If one is used for both purposes, remote control will no longer be necessary and the relays will then seem superfluous. However it is best to mount them both on the board just in case!

In addition, the T2 and T3 controls provide useful visual information about what is actually going on. The green LED lights when data is being read and the red LED is lit when data is being written.

The section in figure 2 between the data input J1 and the input of N38 (pin number 9) is next on the list. This is the circuit around IC6 and IC7 which will undoubtedly look very familiar to KIM operators. It is in fact similar to part of the KIM hardware, albeit improved, because we didn't feel like reinventing the wheel.

Before discussing IC6, IC7 and co, it is useful to know that the data is recorded on tape in the form of a series of audible signals. These are rectangular in form, a 3600 Hz signal being followed by a 2400 Hz one, and so forth, A frequency of 2400 Hz corresponds to a low level bit (logic Ø) while 3600 Hz corresponds to a high level bit (logic 1). The circuit around IC6 and IC7 makes sure the output of IC7 is high when there is a frequency of 3600 Hz at the input J1 and that it is low when the frequency at the input is 2400 Hz. The software of RDTAPE distills either a zero or a null from each cycle. depending on the 3600 Hz time in relation to the concluding 2400 Hz time. Together with the associated

components the circuit around IC6 constitutes a PLL (Phase Locked Loop). To explain this in great detail (with complex formulas) would fill the pages of Elektor for a whole year! We hope readers won't mind if instead we describe its operation very briefly.

Where the interface card is involved, the PLL may be regarded as a frequency follower. This is because it is similar to an emitter follower, where the output voltage imitates the input voltage, an internal oscillator here adapts its frequency to that of the input signal within a certain frequency range and above a minimum level of the input signal. The internal oscillator produces a frequency that is proportional to a control voltage (VCO). Without the input signal the frequency is about 3000 Hz, so exactly half-way between the 2400 Hz, If the frequency at the input is 3600 Hz, the frequency will rise by 500 Hz; at 2400 Hz this will drop by 600 Hz. The control voltage has to be increased for the frequency to drop and lowered for it to rise. Thus, the level of the control voltage is directly related to the frequency of the input signal and after comparing it to a fixed voltage it allows a logic distinction to be made between the two frequencies: locia 1 for one frequency and logic Ø for the other. This is in accordance with the FSK (Frequency Shift Keying) principle.

The PLL is supplied with a +12 V voltage by means of D2 +D3 and C8 which are connected in parallel for transient suppression. The 'clean' 12 V (about 11 V due to the diodes) is also used to preset the input DC voltages (pins 2 and 3 of IC6) by way of R21...R24. In the KIM a 5 V supply is used and any interferance will pass is used and any interferance will pass.

Figure 2. The circuit diagram of the interface card. Part of the circuit adapts the computer to RS 232 standards and part of it establishes communication links between the computer and two cassette recorders.

directly into the (in theory balanced) inputs. Another difference with the KIM is that the input signal is not attenuated by a factor of 10 until it reaches pin 2. All these improvements make the equipment so easy to work with that you'd have to be very careless to make a mistake when inputting data. Look out for 'drop outs' on the tape, dirty or maladjusted recording heads, etc. We happened to discover once after a perfect data entry - that the ground connection between the computer and the recorder was missing! Only pin 2 of IC6 (a kind of differential amplifier input) is used as an asymmetrical control. The system is connected to J1 via C1 which has a much lower value than the KIM in order to filter out the maximum of frequencies below 2400 Hz. Resistor R37 is needed in case the loudspeaker output (or headphone output) of a cassette recorder is employed.

In the absence of an input signal the VCO frequency is set by C3, R25 and P1. It is very important to preset P1 correctly, as this largely determines the quality and reliability of the data reading. Various methods will be stipulated for the correct adiustment of

P1 in a later article.

Pin 7 of IC6 forms the output of the PLL, This supplies the control voltage, which was considered previously, to make sure the VCO frequency is proportional to the input signal. This pin is connected to +12 V by way of C9. Together with a 3K6 resistor inside the IC the capacitor constitutes the loop filter. This enables the PLL to react well to changes in frequency at the output without getting 'over emotional' (overshoot). By way of the ladder filter consisting of R26...R28 and C5...C7 the output of the PLL is connected to

the negative input of the comparator IC7. Its positive input is connected to a fixed direct voltage produced by IC6 (at pin 6) via R29.

The values of the components in the ladder filter depend on the speed at which the 3,6 kHz and 2,4 kHz and 1,5 kHz

As you will remember, increasing the VCO frequency to 3.6 kHz caused the output voltage at pin 7 to drop and decreasing it to 2.4 kHz caused the voltage level to rise. Thus, since the

filtered output of ICB at the inverting input of ICD is either higher or lower than the DC level at its non inverting input, this can be expressed as 'high' (+5 V, via R31) when the input frequency is 3.6 kHz and 'low' (practically grounded) when the input frequency del that is exactive what is required. The output voltage of ICD is inverted by way of N38 ('high' goes 'low' and vice versa) and is applied to PBT.

N.B. There is a limit to the speed at a which the PLL can react to a change in input frequency. Consequently, the output of IC7 will not turn over in one output of IC7 will not turn over in one go from logic 1" to 0" or vice versa, but will fluctuate between the two levels before eventually making a definite thochoce. This is called PLL litter and depressed. Don't worry, subroutine RDTAPE's software knows how to handle such behaviour.

#### Connecting peripherals by means of the RS 232C

The small circuit at the top left-hand corner of figure 2 is surprisingly straight-forward, considering the enormous possibilities that it has to offer, For it enables highly complex peripheral equipment to be connected to the Junior Computer. It consists of a data data of the consist of a data and the computer of the consist of a data of the consist of a data of the computer. It consists of a data of the consist of a data of the computer of the consists of a data of the computer. The consists of a data output. The receiver is situated around 11 and a few other components. T1 converts logic ones at the input (top of S5) into logic zeros and vice versa.

If we suppose that input 6 of N37 is connected to +5 V by way of R8 and forget about wire link P-Q for the moment, N37 will invert the input level received from PBB and its output will control the comparator IC8 by way of R10. A comparison is made with the

voltage at the junction R11/R12/C12. If the output of N37 is logic 1, the output of IC8 will be about +12 V and -12 V when N37 is logic Ø. Again, it can be seen that the output signal of PBØ is inverted irrespective of whether the logic levels are adapted to any particular voltage (+ and -12 V) or not. The data input (via R5) and output (IC8) are connected to a standardised 25 pin D connector, the RS 232 connector. This number refers to the universal standard that has been established for data communications, Each byte is preceded by a start bit to indicate that it has started to be transmitted. The bytes are coded according to the ASCII code.

The RS 232 standard determines the two possible logic levels and their corresponding voltage values. Later on the D connector itself was included in these standard levels. A logic zero is represented by a voltage between +5 V and +15 V (RS 232C version) and a logic one by a voltage between -5 V and -15 V. In the Junior Computer this is about + and -12 V respectively. In other words, a low voltage corresponds to a 'high' logic level and a high voltage to a 'low' level. This is known as negative logic. By inverting the logic levels in the interface twice both during transmission and reception, however, the computer does not have to bother with such subtle distinctions. The D connector features a number of pins that are interconnected. These links may be changed to suit the peripheral equipment. The first suitable device that springs to mind is the Elekterminal, a video terminal with an ASCII keyboard which was originally designed for the SC/MP, but which is equally suitable here. The system program PRINTER MONITOR is based on using the ASCII keyboard as an input (through various key commands) and the actual

Elekterminal or a suitable printer (not at least not for the moment – the metal foil printer published several months ago in Elektor) as an output (display). Now all the hardware involved in the extensions has been discussed, apart from the 'revised' Junior Computer power supply and a few other modifications which need to be made to the main board. These will be dealt with in the article on the constructional details (in next month's issue) and, of course, in Book 3 which should be available soon.

can be programmed by the reader with the aid of circuit no.97 in the Summer Circuits' Issue '80 or purchased ready programmed from Technomatic Ltd. Various pin compatible PROMs are suitable, such as the 74S188, but these cannot be programmed using the above circuit.

#### Table 1

The contents of the PROM IC7. This

### - and let them talk to you

According to people in the know, the first mass-produced type-writer with speech entry will be available in less than two years' time. In addition, special devices are being developed to read aloud to the blind and to teach the deal-mute to speak and read. This the deal-mute to speak and read. This of speech synthesis and then with methods to develop a computer's "hearing' and vocal faculties."

#### Once upon a time . . .

It all started in the Alps of all places, where an ancient instrument, similar to a mouth organ and often used in Alpine

pronounce the individual sounds, or phonemes, that constitute each word. For example, the word one is made up of three phonemes (w.A-m. he bilabial w., the vaguely palatal \( \lambda \) (uh) wowel the smallest possible speech elements, a machine should be able to pronounce any word in a given language once it has mastered all the sounds and, with practice, it could even learn to say whole sentences, which is exactly what thirties.

The block diagram in figure 2 shows the remarkable voder. A pulse generator rich in overtones provides the raw

# talk to computers

Everyone takes it for granted nowadays that merely depressing a button is enough to make a washing machine do the week's washing 'at the drop of a hat', or a scanner acknowledge your credit card without the need for a telephone call to the bank. Just imagine what it would be like if computers 'evolved' vet another stage further forward and the washing machine could be activated by a mere word! Sounds like something from 'Star Wars': talking automats that advise you on investments and give you the latest from the Stock Exchange and tell you to 'put your money where your mouth is' . . . Seriously though, experiments are currently being carried out to equip computers with hearing and speech faculties. This would enable machines to be used for increasingly complex purposes in the future, without their being operated by electronic experts. In other words, the idea is to bring computers much closer to everyday reality.

folk music, has been emitting vowel-like sounds (a, e, i, o and u) for donkeys' years. In contains a metal 'tongue' which vibrates within a metal frame whilst the player grips the frame between his/her teeth and shapes sounds with the hollow cavity of the mouth. Thus, the mouth becomes a resonant chamber in which the vowels are formed. As early as 1936 K.W. Wagner hit on the idea of using this principle to construct an electrical speech synthesiser. Figure 1 shows the result in the form of a block diagram. It consists of a pulse generator that is connected to a series of formant filters. This simple device was able to imitate all the vowels and several voiced consonants (111, mmm, nnn, rrr) surprisingly well.

A few years later, H. Dudley at the Bell Telephone Laboratories managed to go one step further: based on the Wagner device he built the 'voder' (voice operated demonstrator) in 1939. This speech synthesiser could successfully minister all the vocal sounds, provided it was skillingly operated. The voder pawed the way for modern speech synthesisers and so it is well worth a closer examination. For this we must make a quick dash to the nearest telephone.

When we ring up to find out what time it is, a voice owns on the other end and drones out the time after every thirty seconds. We wonder whether it belongs to some wretched creature whose job it to some wretched creature whose job it to both the contract of the contract

Thus, if a machine is already capable of being programmed to 'say' separate words, it must obviously be able to

material for voiced sounds and a noise generator produces the unvoiced ones (f. s, sh, etc.). A series of filtes connected behind the generator of the sound of t

a filter with a lower frequency. Several of the filter keys switches belonging to the voder are individually linked, so that more than one formant range can be activated at once. An auxiliary key ('soft') turns down the volume for unvoiced consonants.

Finally, there are three keys for socalled 'explosive' consonants which can be switched either to voiced (d, b, g) or to unvoiced (t, p, k). (They are called 'explosive', as each requires a slight burst of air pressure — behind the teeth in the case of d and t, behind closed lips for b and p and at the back of the throat for g and k.)

Obviously human speech is not made up of sounds alone. For one thing man is much more musical than a rusty robot and intonates while he talks. That is why a pitch pedal has been included in the device.

As figure 3 shows, the voder is such a complicated device, all things considered, that the operator has to be a real artist to be able to control it skilfully. The ideal solution is therefore to make it fully automatic, which is what most speech synthesisers are novadays, which side being reduced to that of a Eurocard has recently shrunk to that of an IC.

#### Modern results

Until now speech synthesisers have belonged to two categories: word generators which store whole words in

Figure 1. The first electronic device to produce individual speech sounds (by K.W. Wagner 1936).

2

over a great distance, or speaks with his mouth full, or on a faint telephone line, it is surprising how much the listener is able to understand.

The word generator principle does have certain disadvantages:

The covabulary cannot be extended 'per program'. Although ROMs can be provided with a specific vocabulary, any modification or extension to it will mean having to manufacture an entirely new ROM. Thus, when the device is confronted with anything beyond its scope, it will be totally 'speechless'.

2. The total available vocabulary is very limited, about 250 words at the moment. Even for this small amount National Semiconductor's 'Speech Processor Set' needs 128 kbit and that is

roles georetic trade)

with a second second

Figure 2. The block diagram of the voder built at the Bell Telephone Laboratories in 1939 by Homer Dudley. This device was capable of reproducing the full range of phonemes, but as it was manually operated, the result depended largely on the operator's capabilities.

memory and phoneme generators which can shape individual vocal sounds before joining them up into words.

#### Word generators

Storing whole words in semiconductor memories (ROMs) did not become feasible until component prices dropped and memories could be extended in a compact manner. The words are all digitalised before entry, stored in memory and then allocated to specific addresses. This enables full sentences to be formed be merely accessing the word addresses to a certain order. It has the additional advantage that anyone can program sentences without being an expert in phonetics, as they are typed in on an ordinary type-writer keyboard.

It is, however, highly uneconomical to simply digitalise speech signals by means of an AID converter and then store the bits in ROMs or RAMs. This leads to between 50,000 and 10,000 bits of data per speech signal second I Fortunately, the human language features great "redundancy", that is to say great "redundancy", that is to say sentence, the remainder will be enough to carry the "gist" of the idea across. Whether one person yells at another

Figure 3. The voder (Voice Operation Demonstrator) 'keyboard'. The manual controls a series of formant filters and the operator has to be a talented 'performer' for the sounds to be coherent.

reducing memory space to an absolute minimum using all the methods described above.

3. Any sentence is highly complex in structure. It is not just a string of correctly articulated sounds, but it also involves varying the intonation and pitch, breathing spaces and emphasising certain words or sounds. These parameters are not fixed in any way, but depend on the context within which the individual words are placed. A question, for instance, sounds very different to a statement, even though the question mark cannot be 'seen'! A child soon learns to lower the pitch of his/her voice at the end of a sentence. This cannot be done by a word generator, however hard it tries, because each word is stored as a totally neutral entity in the ROM, so that the machine is bound to sound like a robot when it 'speaks',

#### Phoneme generators

This type of speech synthesiser is largely based on Dudley's voder, as it is built up on a series of voiced/unvoiced tone generators, formant filters and pitch controllers. In addition, however, phoneme generators contain memory locations storing algorithms to produce each individual phoneme. When an instruction to form a particular phoneme appears at the input of the speech block, all the parameters are set to transform the generator signal into the required sound. Depending on how complex the sound is, up to ten parameters may be needed simultaneously (pitch, intonation, duration, 1-4 resonance filters, voiced/unvoiced, etc.).

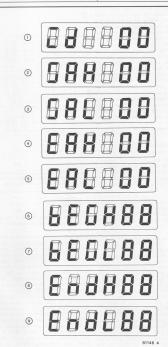

The machine may be programmed with a standard vocabulary, and then an additional memory includes the individual phoneme codes used for each word. Its great advantage is that it can produce any sound in a language family and so, theoretically, it should be able to master the entire vocabulary of all those languages. The Anglo-Saxon language consists of 64 phonemes group altogether - that is all that is needed to reproduce every word in both English and German. An example of a phoneme generator is the VOTRAX VS-6.0 which organises each phoneme command in the form of an 8 bit data word. 6 bits serve to select the required phoneme and 2 bits produce the right pitch, so that the utterance sounds fairly natural. The 64 phoneme codes also contain various stages in intonation and speed for every sound. The phoneme commands for the VOTRAX SC01 speech synthesiser are shown in table 1. A sound may vary in length from 250 ms for the longest phoneme to 47 ms for the shortest.

Instead of using different resonant filters as the sentence progresses, the intonation may also be varied by 15 filters connected in parallel with preset frequencies for each one. The voiced/ unvoiced tone signal produced by the tone oscillator or noise generator

Photo 1. The VSM 2032 speech module from General Instrument incorporates a full-fledged speech synthesis system on a compact card. It consists of an interface, a speech generator IC, the SP 0250, a ROM and an NF amplifier.

SP0250

Photo 2. The SP 0256 from General Instrument takes speech synthesis one step further than its SP 0250 counterpart (see photo 1). Again, it consists of a generator that includes a word memory, only now it also includes a 16 K mask programmed ROM. In addition the IC is able to address up to 491 K of external ROM.

respectively acts as the input signal. Behind each filter there is a voltage controlled amplifier (VCA) which enables

the sounds to change in nature and determines the contribution of every frequency range to the output signal, in the same way as in a vocoder.

The speech synthesiser also features Linear Predictive Coding (LPC) which ensures great linguistic flexibility and an unlimited vocabulary.

Combining phoneme generators and word generators reduces the need for a huge memory capacity and enables 'allophones' (transitions between phonemes) to be produced, which makes the machine sound more natural.

Phoneme generators are a little more difficult to program than word synthesisers, as each sound has to be phonetically transcribed before entry and there is a great discrepancy between the written (orthographical) and the spoken language. Thus, the operator must be up to date with phonetics and

an ordinary alphabetical Keyboard is no longer valid. In America this problem has been solved by developing special programs which phonetically transcribe typed-in language. This means that constantly changing information such as Stock Exchange reports, railway time-tables, road reports, etc. is now much easier to reproduce.

#### Which system is likely to survive? Let us compare word and phoneme

Let us compare word and phoneme generators and see which type is likely to stand up to the test of time.

Word generators signal digitalisation using partial data reduction

$\begin{array}{c} \text{(bits per second)} \\ \text{signal digitalisation using all} \\ \text{reduction techniques} & \pm 600\text{-}800 \text{ bps} \end{array}$

± 2000 hps

Phoneme generators

their metallic sound

Linear-Predictive-Coding ± 1200 bps Phoneme generators such

as the voder 70 bps

As you can see, the voder type of phoneme generator requires very little memory capacity, as it features high speech redundancy. Since chips are getting cheaper all the time, however, word generators will probably gain popularity once their vocabulary can be increased to over 500 words despite increased to over 500 words despite

#### Sources:

Pedro the Voder, a machine that talks. Bell lab. Rec. 17 (1939) The Voder, Electrician.

London 123 (1939) Rabiner, L.R. Computer Synthesis of Speech by Concatenation of Formant-

Coded Words.

Bell System Technical Journal (1971)

McIlroy, M. Douglas. Synthetic English

Speech by Rule. Bell Telephone Laboratories Inc., Murray Hill N.I.

Teja, E. Voice Input and Output. EDN November (1979)

News Releases from:

Computalker Consultants Box 1951, Santa Monica CA 90406 Telesensory Systems

3408, Hillview Ave, Palo Alto CA 94304 Votrax Div of Federal Screw Works 500, Stephenson Hwy, Troy Mi 48084