107

### contents

selektor

| Teedback pill for fm In a previous size of Elektor the theoretical background of a Feedback Phase-Locked Loop (P.L.I. tuner was discussed (Elektor 3, p. 412). A practical design is now described for a complete receiver, including audio ampliffers, which provides high performance at a moderate cost.                                                                                                                                                                                                                                                                                                                                                                                                                                               | 110 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| to drive or not to drive $\dots$ – C.J. Both The slower reactions of a person 'under the influence' form the basis of this 'drive'/'no drive' tester.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 119 |

| optical-lock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 122 |

| sixpence detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 123 |

| function generator ic 2206  Function generating ICs have been on the market for several years. Now one can refer to a 'second generation' of these ICs, for technical progress has resulted in improved performance at only slightly higher prices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 124 |

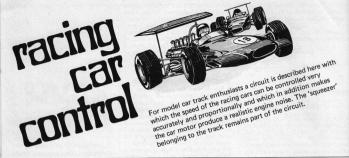

| racing car control  For model car track enthusiasts a circuit is described here with which the speed of the racing cars can be controlled very accurately and proportionally and which in addition makes the cer motor produce a realistic engine noise. The Squeezer belonging to the track remains part of the circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                 | 128 |

| mini-mw                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 130 |

| battleships — R. ter Mijtelen  This article describes an electronic version of the well known game of 'battleships'. The pencil and paper have been replaced by switches and LED's — under the control of a boxful of TTL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 131 |

| led fm scale                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 134 |

| alarm  An alarm which gives its alarm signal at certain repetitive times, does not need to know what the actual time is. It is sufficient if it can measure the time between the alarm time points (for instance 24 hours).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 135 |

| capacity relay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 138 |

| pin the tail on the donkey                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 139 |

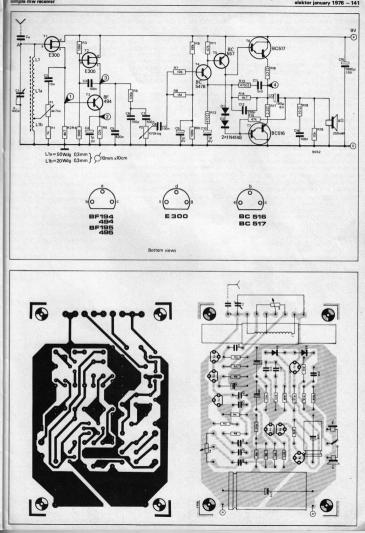

| simple mw receiver The alignment of superhet receivers presents problems that may deter some enthusiasts from undertaking their construction. A simple MW superregenerative receiver presents no such difficulties, and the results obtained can be quite satisfactory when one has achieved the necessary "douch" for the reaction control.                                                                                                                                                                                                                                                                                                                                                                                                              | 140 |

| stereo led level meter.  The Texas IC type SN 16880 N contains all the functions necessary for a stereo LED level meter, which can replace the conventional n.oving coil instrument in tape recorders or audio mixers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 143 |

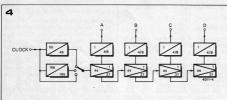

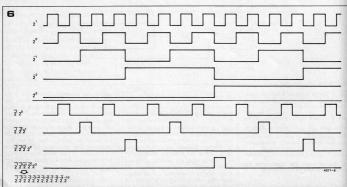

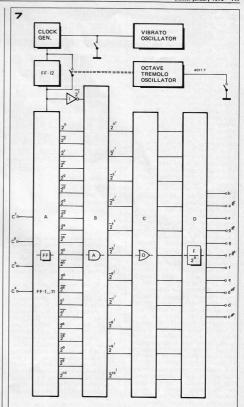

| digital master oscillator (1)  The use of frequency dividers in electronic organs has been known for many years. The usual procedure is to use divide-by-two stages to divide down the notes of the highest octave to obtain the lower octaves. Until use of the control of the process of the top octave. The on normal practice to use travele independent master oscillators for the twelve notes of the top octave. The one of the top octave. The one of the top octave of the top octave of the top octave of the top octave of the top octave. The other octave of the top octave of the top octave and the octave of the top octave and the octave of the top octave and divided from a single clock generator, unfer form on such disadvantages. | 144 |

| missing link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 148 |

| high security burglar alarm sensor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 149 |

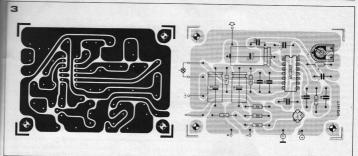

| pill-ic stereo decoder In response to popular demand we publish this design for an FM stereo decoder using the Motorola MC 1310 P. Although nothing is claimed for this circuit by way of originality (if must have been published in some form hundreds of times) it is nevertheless a useful design utilising a device that has become virtually an industry standard.                                                                                                                                                                                                                                                                                                                                                                                  | 150 |

| elektor shorthand                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 152 |

| tup-tun-dug-dus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 153 |

| market                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 154 |

| linear ics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 157 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15/ |

# feedback pll for fm

In a previous issue of Elektor the theoretical background of a Feedback Phase-Locked Loop (PLL) tuner was discussed (Elektor 3, p. 412). A practical design is now described for a complete receiver, including audio amplifiers, which provides high performance at a moderate cost.

Measurement results: (fmod = 400 Hz, deviation = 40 kHz): Mono: 3.2 µV at 87 MHz and 35 dB S/N. 2.0 µV at 100 MHz and 35 dB S/N. Stereo: 20 UV at 94 MHz and 26 dB S/N AF output level (f<sub>mod</sub> = 400 Hz, deviation = 40 kHz. fc = 94 MHz): Approx. 130 mV RMS. AM suppression (deviation = 40 kHz, 30% AM, f<sub>mod</sub> = 400 Hz): V<sub>in</sub> 3 μV AM suppression 50 dB 25 µV 53 dB 50 µV 53 dB 100 µV 53 dB 400 µV 53 dB 1 mV 48 dB 2 mV 44 dB Hum level (in metal case): 70 dB.

Although many years have passed since the introduction of FM broadcasts in the U.K. it is only recently, with the advent of stereo broadcasting, that interest has really been aroused in this medium. Until now a high quality FM receiver has been either too complicated or too expensive for the home constructor to build. These problems are overcome by the use of PLL techniques in the receiver described here described here described here described here.

The front-end used in this design (i.e. the r.f. and mixer/oscillator section) is a ready-built unit. It is the front-end that determines, for the most part, the usable sensitivity of the receiver, which in this case is about 2.5 µV. It is possible, in principle, to use other front-ends in this design, but the rest of the receiver will have to be adapted and this procedure should be undertaken only by those with the necessary theoretical knowledge. As with other modern re-'locking-on' to a transmission once it has been tuned to it, but while normally a special Automatic Frequency Control (AFC) circuit is built into the receiver for this purpose, the PLL receiver has this capability inherently. The feedback PLL receiver 'captures' the transmission and adjusts itself continuously to follow it in frequency. Thus the AFC does not operate in the usual way and in fact the AFC input to the front-end forms part of the detector circuitry. As an additional bonus it is possible to reduce the bandwidth of the feedback PLL receiver. This is helpful when listening to a noisy mono transmission, for instance,

### prove the signal-to-noise ratio. Principle of operation

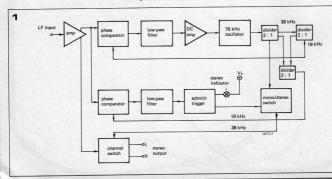

Referring to the block diagram of figure I the tuner operates as follows: in the front-end a band of frequencies from the aerial input is amplified and then mixed with the oscillator signal (B). As a result of this mixing two new frequencies come into being that are the sum and difference of the two original frequencies. For example, if the in

when reducing the bandwidth will im-

Figure 1. Block diagram showing the Feedback PLL principle.

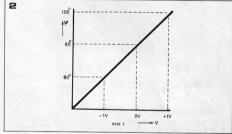

Figure 2. Graph of phase difference versus phase comparator output voltage.

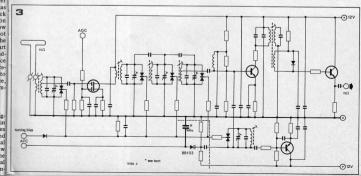

Figure 3. Circuit diagram of the Toko EF5600 front-end module.

RP X B VCO XTO DO Mits dem out

coming aerial signal has a frequency of 100 MHz and the oscillator frequency is 110.7 MHz then two new signals appear at the mixer output with frequencies of 210.7 MHz and 10.7 MHz respectively. The mixer output is filtered to remove the unwanted components and the 10.7 MHz is amplified by the i.f. amplifier, which is a tuned amplifier with a passband centred on 10.7 MHz. It can thus be seen that the receiver can be tuned by altering the passband of the aerial input stage and by altering the frequency of the oscillator. This is, of course, normal superhet practice, which those familiar with r.f. techniques will recognise.

cuit differs from more conventional receivers. The output of the if, amplifier is fed to a phase comparator (D). The other input of the phase comparator is fed by a high-stability 10.7 MHz signal from a reference oscillator (F). The characteristics of the phase comparator are shown in figure 2. If the phase difference between the if, output

From here on the operation of the cir-

ds

al

a

ol

and the reference frequency is greater than 90° the output voltage is positive, if it is less than 90° the output is negative. At 90° phase difference the output voltage is, of course, zero.

However, since the input signal to the

aerial is frequency-modulated the only way to keep the phase difference between the i.f. output and the reference oscillator constant is to vary the frontend local oscillator so that it 'tracks' the signal. A constant 10.7 MHz output is

16

12

8

4

SPECIFICATION FOR FM TUNERHEAD TYPE EF5600

| Frequency range         87 - 109 MHz           Supply voltage         +12VDC           Current         17 mA max           Input impedance         75 ohms           Output impedance         75 ohms           Power gain         30 d8 min | Temperature stability         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| Image/IF/Spurius                                                                                                                                                                                                                             | AGC operation (+2.5 to -2.0V) |

100 102 104 196 108 MHz

56- 4

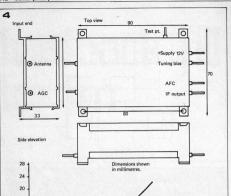

Figure 4. Outline, pin connections and specifications of the EF5600.

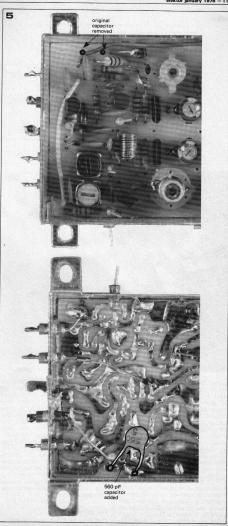

Figure 5. These photos show how the modification to the AFC input is carried out

then produced. This tracking is achieved by feeding the output of the phase comparator back to the AFC input of the front-end so that it attempts to maintain a constant 90° phase difference between the if. output and the reference socillator by varying the local oscillator frequency. The output voltage of the phase comparator is thus a replica of the original modulation of the input signal it still remains, of course, to extract the stereo information.

### The tuner

The tuner used in this design is a Toko type EF5600. It is one of the best tuners generally available for the home constructor. The circuit is given in figure 3, and the outline, specifications and pinning are shown in figure 4.

The input stage utilises a dual gate mosfet, which has good linearity — even strong input signals will give rise to very little cross modulation. This RF praamplifier stage is followed by three tuned bandpass filters, capacitive coupled. The selectivity of these filters is sufficiently high to make it possible to use a simple bipolar mixer stage.

It is common practice in FM front-ends to take the IF output straight from the secondary winding of the IF output transformer. In this design, however, an extra output stage has been added. This has the advantage that the (tuned) IF coil is scarcely loaded by the IF strip, which means that there is never any need to retrim the coil — no matter what - the input impedance of the IF strip is. The tuner is fully aligned at the factory, and one should resist the temptation to twiddle any of the trimmers or cores.

The only modification to the tune needed for use in the feedback PLL design described here is the AFC input. In the original tuner, this input is de coupled with a 10 n capacitor. This must be removed, and a 560 p capacitor soldered in its place (see photos, figure 5). It would be nice if Toko could supply tuners with this minor modification already built in ...

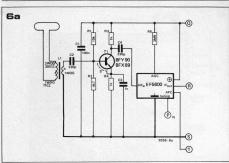

The Mark I version of the feedback PLL receiver proved to have an input sensitivity of 8 µV. To improve this, an additional R F preampifier stage was added (figure 6a). The input transformer can be wound on a HF type ferrite bead, using 0.2 mm (36 SWG) enamelled copper wire (figure 6b). If required, both the 75 Ω and the 300 Ω winding can be wound on the same coil.

### The i.f. Amplifier

An unusual feature of the i.f. amplifier is the absence of bandpass filters. These are omitted because the tuner tisself provides good selectivity and because the PLL has inherent selectivity and to the 10.7 MHz reference oscillator so that it can only lock onto 10.7 MHz. In addition, as the i.f. amplifier is within the feedback loop any filters would have to meet stringent phase distortion criteria, which is another reason for omitting them.

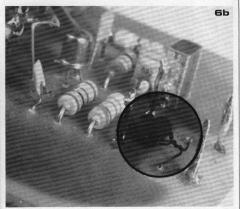

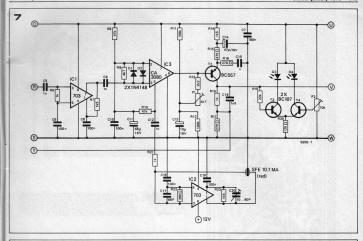

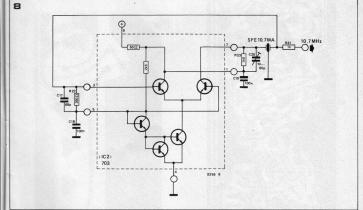

The IF signal is amplified by IC1 (gain approx, x 40) and fed to the OTA (IC3. figure 7). Diodes D1 and D2 limit strong signals. The first stage of the OTA is used as multiplier for phase detection, so there is relatively little IF amplification. For this reason, the bandwidth of the PLL depends on the input signal strength to the extent that for low signal levels (less than 2 µV) the bandwidth is reduced. This is an advantage when listening to weak transmissions, as it improves the signal-to-noise ratio. The disadvantage is that it can lead to distortion unless the weak transmissions in question were narrow-band to start with. Preset potentiometer P1 is used to set the loop gain, and hence the bandwidth. It is correctly set when a fully modulated stereo transmission is reproduced without audible distortion.

The output impedance of the OTA is relatively high, so a buffer stage (T2) has been added. The RC networks associated with this transistor are compensation networks for the loop.

The holding range of the PLL is so large (certainly for strong transmissions) that some form of tuning indicator is re-

quired. This is the function of T3 and T4. If there is no signal present at point 'R' (output of the tuner) the voltage at the collector of T2 is approximately 3.6 V. P2 is now set so that D3 and D4 light equally brightly. When tuning in to a transmission, the DC voltage on the collector of T2 varies in such a way that D3 lights if the tuning is off to one side and D4 lights if the tuning is off the other way. When the receiver is tuned in correctly both LEDs light equally.

### The 10.7 MHz oscillator

In the interests of economy a 10.7 MHz ceramic filter is used as the frequency determining element in the oscillator instead of a crystal (figure 7, also shown separately in figure 8). This filter is connected between pins 3 and 7 of IC3.

The oscillation frequency is determined by the ceramic filter: it is simply the frequency at which the phase shift of the filter is 0° (or 360°), However, most ceramic filters do not have 0° phase shift at their nominal frequency so some phase compensation is necessary. For this reason C17 and C20 have been added. C20 is a trimmer, so that the frequency can be set at exactly 10.7 MHz provided one has access to a frequency counter. However, this is not so critical: if no frequency counter is available C20 can simply be set in the middle of its range.

The (reference) output signal is taken from pin 3, as this gives a cleaner sinewave than the output at pin 7.

#### The stereo filter

The stereo multiplex signal consists of

#### Parts list

Resistors: R1, R41 = 10 k R2.R9.R31\_R36\_R37 = 4k7 R3,R4,R6,R16,R21,R34,R35 = 1 k R5 = 3M9R7 R14 R23 = 1k5 R8.R10 = 47 k R11,R12,R39,R40 = 100 k R13.R32 = 2k2 R15 = 470 Ω

R17,R18 = 270 Ω R19 = 22 k R20 = 120 Ω R22 = 390 Ω

R24.R25 = 470 k R26,R28,R29,R30,R33 = 15 k R27 = 330 () R38 = 27 k

R42 = 56 k R43.R44.R45 = 560 Ω R46 = 150 Ω/2 W P1 = 47 k preset P2 = 10 k preset

P3 = 4k7 preset P4 = 220 k preset P5 = 2k2 preset P6 = 22 k multiturn

$C11 = 68 \mu/16 V$

### Capacitors:

C1,C6,C7,C8,C10,C18,C19,C45,C46 = 100 n C2.C4 = 220 p C3,C5,C9,C12,C15 = 1 n

C13.C36.C37.C38 = 10 u/16 V  $C14 = 47 \mu/16 V$ C16 = 1n8 C17 = 68 p

C20.C22 = trimmer 10 . . . 60 p C21,C32 = 470 n C23 = 150 p

C24.C25.C26 = 120 p C27 = 47 p C28 = 2µ2/16 V

C29 = 47 n C30 = 470 pC31,C34 = 220 n

C33,C35 = 10 n C39 = 470 µ/25 V C40 = 47 µ/6 V

C41,C42,C43,C44 = 470 µ/40 V

Semiconductors: T1 = BFY90, BFY89 T2,T6 = BC557

T3,T4,T7 = BC107 T5 = BC547B D1,D2 = 1N4148 D3,D4,D5 = LED

D6 = ZTK22 (22 V) (see text)

B = 4 x 1N4001 IC1.IC2 = 703 IC3 = CA3080

IC4 = MC1310P IC5 = TBA625B

Sundries L1 = ferrite bead (see text) ceramic filter SFC 10.7 (red dot) S1 = switch, SPST meter = 400 µA fuse = 100 mA TOKO-tuner EF5600

Figure 6a. The RF preamplifier stage and Toko front-end.

Figure 6b. The aerial transformer: a ferrite bead.

Figure 7. The circuit of the 'IF stage and detector' and the tuning indicator LEDs.

Figure 8. The 10.7 MHz reference oscillator (also shown in figure 7).

three components:

an AF signal from 30 Hz to 15 kHz;

a double sideband suppressed carrier signal centered around 38 kHz, from

signal centered around 38 kHz, from 23 kHz to 53 kHz; - a pilot signal, derived from the orig-

inal 38 kHz carrier, at 19 kHz. It can be shown that stereo decoders will not only detect the signals in the 23 to 53 kHz band, but also other (unwanted) signals centered around multiples of 38 kHz. For the best signal-to-noise ratio it is thus important that no signals above 53 kHz are fed to the stereo decoder. To this end, the filter shown in figure 9 has been added. The best channel separation is obtained when the phase shift at 38 kHz is zero degrees; this can be set with C22. For this adjustment it is best to use a strong

118 - elektor january 1976

(local) transmission or a stereo test generator. C22 is simply set for maximum separation.

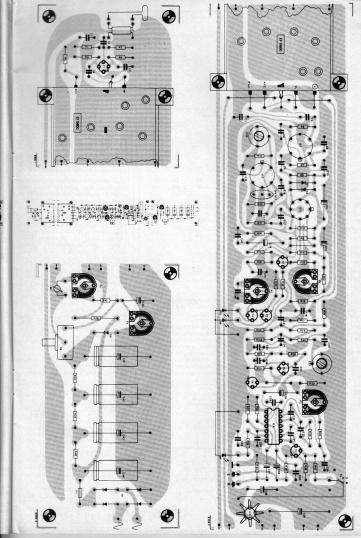

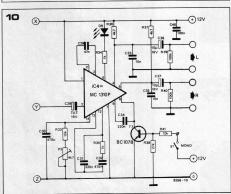

### Stereo Decoder

The stereo decoder (figure 10) uses the now commonplace Motorola MC1310P PLL IC and needs little explanation.

The only setting up required with this type of decoder is to tune the oscillator so that the free-running frequency is 19 kHz. This is accomplished by means of P3. The channel separation is about 40 dB. A LED (D5) is included as a stereo indicator beacon. The decoder outputs provide nominally 100 mV

Figure 9. The stereo filter.

Figure 10. The stereo decoder.

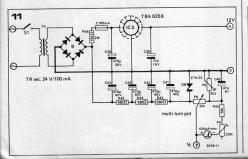

Figure 11. The power supply, including the smoothing and stabilisation for the tuning voltage.

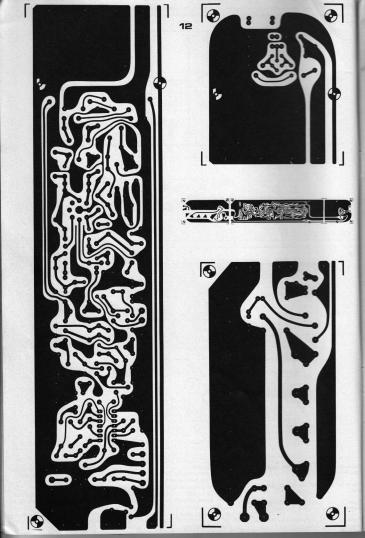

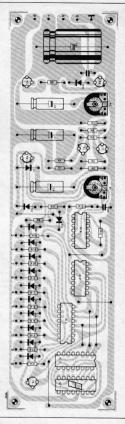

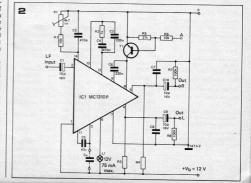

Figure 12. The p.c. board for the complete receiver, including front-end, stereo decoder and power supply (figures 6a, 7, 9, 10 and 11). Note that the board consists of three sections that are joined together with wire links

Figure 13. Pin configurations of the two types of ceramic filter.

Figure 14. A typical tuning scale meter calibration.

which should be adequate to drive most amplifiers. The amplifier input impedance should be not less than 22 k.

### The power supply

The receiver is relatively insensitive to variations in supply voltage, so that a fairly simple power supply circuit can be used (figure 11). The resistor (R46) in series with the stabiliser IC reduces the power dissipation in the IC and, at the same time, keeps its input voltage safely below the maximum value (24 V). The tuning voltage must be derived from a well smoothed and temperatureindependent supply. This consists of C41 to C44, R43 to R45, and a temperature compensated zener diode (D6). If the ZTK22 is difficult to obtain any other 22 V zener can be used, provided it is temperature-compensated. If there is any doubt on this score, however, it is advisable to use four 5.6 V voltage reference diodes in series.

#### Construction

The parts list gives details of all the required components. Equivalent types are given where possible. The p.c. board

to drive or not to drive

and component layout are given in figure 12.

Both SFC and SFE type ceramic filters can be used; in both cases they should carry a red dot which shows that they are exact 10.7 MHz types. The pin configurations of the two types of filter are different (figure 13), but the board will accomodate both types. The Toko CFSA 10.7 filters can also be used; the pinning corresponds to that of the SFE 10.7 MHz. For these filters 'no colour code' denotes an exact 10.7 MHz type.

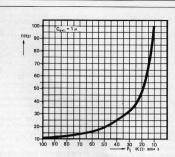

A cheap moving coil meter can be used for the tuning scale; it measures the tuning voltage, but the scale can be calibrated in MHz. Figure 14 gives an example. The actual calibration can be done either by tuning in to several known transmitters in succession and marking them on the scale, or else by measuring the tuning voltage and calibrating the scale in accordance to the graph shown in figure 4. An entirely different possibility is to use a slider potentiometer for P6 and calibrate a scale for it in MHz; the tuning meter then becomes redundant.

The front-end should be mounted on the p.e. board and wired to it with stiff links. Connections to the tuning potentiometer and the tuning scale meter should be as short as possible to avoid hum pickup. It is advisable in any case to use screened cable for these leads. Sockets should be used for the ICs, sepecially by the less experienced constructor, to avoid damage during soldering.

### Alignment

When construction is complete (check that the ICs are the right way round in the sockets!) turn Pl and P2 fully clockwise, and set all other potentiometers and trimmers in the middle of their range. Now switch on and check the supply voltages. Do not yet connect an aerial. Alignment now proceeds as follows:

If a frequency counter is available, readjust C20 until the reference oscil-

lator is set at 10.7 MHz. Otherwise simply leave C20 in the middle of its range — the frequency will not be far

Make sure that there is no reception as yet (if necessary, tune away from any station with P6), and adjust P2 until both tuning LEDs (D3 and D4) light equally brightly.

Plug in the aerial. It should be possible te receive some stations by tuning in with P6. Select the strongest stereo transmission available, then turn P1 anti-clockwise until distortion just becomes inaudible. P1 is correctly set when there is no distortion and slight retuning (with P6) produces no change in volume.

Now P3 in the stereo decoder should be adjusted as follows: P3 is adjusted until the stereo LED (D5) lights and is then set to the middle of the range over which the LED is lit.

After this adjustment, recheck the setting of P1 - some minor readjustment may prove necessary.

Next, set C22 for maximum stereo channel separation.

Set P6 at minimum; P5 is now ad-

justed so that the low frequency end of the band is at 87 MHz (tuning voltage approximately 3.5 V).

Finally, with P6 at maximum, P4 is set for full scale deflection of the tuning meter if this is included. The tuning meter scale (or slider potentiometer) can now be calibrated as described under 'construction'.

5)

Driving a car immediately after drinking too much alcohol is asking for trouble - even if one doesn't happen to run into a police check. One could all too easily run into something elsel Most drivers have found that they can drive safely (?) on the recipe 'one glass per hour'. The trouble is that it is so difficult to keep to that one glass - and that the more one drinks the more one's confidence will override the fear

of getting caught, Simultaneously

one's ability to react to a critical

situation correctly and fast will

diminish drastically. The slower

reactions of a person 'under the

influence' form the basis of this

'drive'/'no drive' tester.

### Editorial note:

The author suggests using the circuit to block the ignition in a car. We do not advise the think of what would happen if you stalled your engine in the centre of a busy crossing! However, the unit can be quite useful as a reaction tester in its own right – e.g. to state departing guests after a party, so that taxis can be ordered as required...

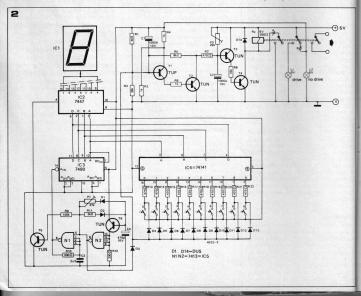

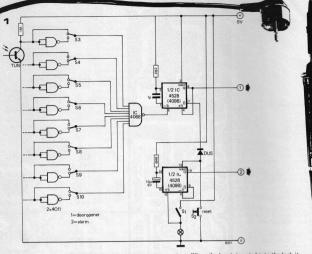

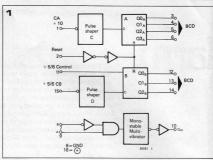

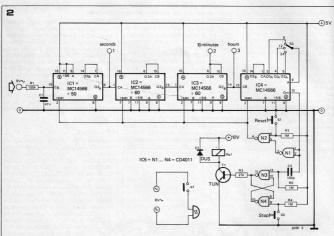

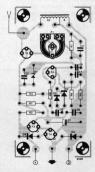

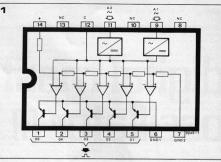

The 'drive'/no drive' tester is provided with ten push-buttons, two signal lamps and a minitron (see figure 1). It is intended to be wired into the starter-circuit, to prevent a slow-reacting would-be driver from actually starting the engine (see didroial note!). The tester is then activated when one turns on the ignition. The device can of course be provided with a mains supply and used indoors (at the end of a party').

What happens is the following: when the ignition is switched on the minitron will display a random numeral. The would-be driver now has to press the corresponding button, as quickly as possible, holding it down until the minitron changes to a different numeral — then quickly press the new corresponding button, etc. After a few of these tests, assuming that they are all performed inside the time limit, a relay

cator will now light up and the engine can be started. If however any reaction time is too long, the 'no drive' indicator will not go out at the expected end the the programme and the starter circuit will remain blocked. Turning off in guiltion will reset the tester (by interrupting the supply), after which the can can be attempted again (if one wishes).

To allow for individual differences in 'normal' reaction time two presets are included, P1 and P2, which respectively control the interval between renewals of the display and the total time taken by the successful test (i.e. the length of time for which one must 'keep it up').

The programming circuit consists of a high and a 'low' frequency oscillator (N1 and N2, respectively, with associated components). The former produces a square wave at a repetition frequency of a few kilohertz, while the latter switches between positive intervals of

less than a second and longer negative intervals that can be preset by P1. The 'low' oscillator is arranged to key the 'high' one off during its negative intervals, so that the result is a series of kilohertz pulse-trains separated by shutoffs of a few seconds duration each.

The kilohertz pulses are counted by the SN 7490 (IC3) and the result presented in BCD form to the SN 7447 (IC2) and SN 74141 (IC4) and SN 74141 (IC4) decloters. The SN 7447 delivers a seven-segment drive directly to the minitron. The SN 7414 (decoder produces decimal outputs (inverse logic! Decoded output is '07), each of which is passed (during the negative intervals) to the reaction timer, vis a resistor and a

diode. As long as one of the decimal outputs is reaching the reaction timer, the lectrolytic (CI) will be receiving a charge. This process can only be interrupted in time by pushing and holding the correct button, which will 'kill' the decimal output concerned. If, on the other hand, CI is charged far enough it will 'fire' the thyristor-like circuit of TI and T2. This Tatch-circuit' will be reset (and CI discharged) at the next positive interval of the 'low' oscillator.

In the meantime the master timeswitch, the heart of this tester, has been ticking away the seconds since the

### Components list:

Resistors: R1 = 6k8

R2 = 39 k

R3.R4.R6 = 1 k R5 = 8k2

R7,R13 . . . R22 = 470 Ω

R8 = 10 k R9 = 100 k R11 = 3k9

R10,R12 = 330 Ω

P1 = 47 k preset P2 = 22 k preset

Capacitors:  $C1,C2 = 1000 \mu/10 V$

C3 = 2n2

C4 = 470 µ/10 V

C5 = 100 n C6 = 1000 u/25 V

Semiconductors:

D1 ... D14 = DUS

T1 = TUP

T2 . . . T6 = TUN

IC1 = 3015 F minitron

IC2 = 7447

1C3 = 7490

IC4 = 74141 IC5 = 7413

Miscellaneous: Re = 6 V/250  $\Omega$  relay (1 break, 3 make)

L1,L2 = 6 V/50 mA lamp

S0 . . . S9 = pushbuttons

power was turned on. It consists of P2. C2, T3 and T4. The interval that must elapse before this time switch fires can be preset by P2. When the electrolytic is sufficiently charged, the current through T4 will cause the relay to attract. This relay will 'hold' via one of its contacts, so that it can only be released by interrupting the power supply. A second contact turns off the tester proper and replaces the 'no drive' indication by 'drive'. The remaining contacts (in parallel) are wired in series with the car's starter relay circuit, so

that they enable the engine to be started.

Whenever a too-long reaction time causes T1 and T2 to latch, the main timing capacitor (C2) will be discharged, essentially restarting the test period. It is only possible to obtain a 'drive' permit after a sufficient number of sufficiently quick reactions has been successively performed. As already noted above, the tester is cleared by a short interruption of the power supply. Bear in mind that the necessary 5 volt supply will have to be derived from a

vehicle battery of which the voltage can drop quite far during starting!

One could spend hours discussing to what extent a piece of hardware can be expected to stand in for the failing sense of responsibility (or lack of self-discipline) of a human being. Perhaps the final remark could be this: use pushbuttons of a recessed type, to prevent the subject of the test from depressing them all simultaneously!

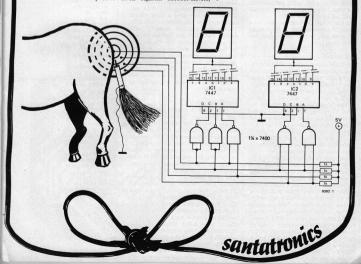

An electronic lock, which is opened using a binary encoded optical key can easily be constructed using 'home-made' phototransistors and CMOS logic ICs. The principle of operation is very simple. The lock consists of a row of phototransistors, which can be illuminated by a lamp. The key is a strip of transparent plastic with sections opaqued to form a binary code.

### The circuit

Figure 1 shows the circuit of the optical lock. For simplicity only one phototransistor is shown, but there are 8, each connected to the input of a NANDgate as is the own shown. Each phototransistor has a 1 M collector resistor. When a transistor is illuminated its leakage current increases and the collector voltage falls. When it is not illuminated the leakage current is very small and the collector voltage is almost equal to supply voltage. The illuminated and non-illuminated states therefore correspond to logic '0' and logic '1' respectively on the input of the NAND gates (connected as inverters).

When the key is inserted into the look it depresses a microswitch (S1) so that the lamp lights (see figure 2). The opaque sections of the key correspond to logic "1", and the transparent sections to logic "0". The outputs of the phototranistors thus assume the binary code. Switches S3 to S10, which are used to set up the coding of the lock, are so arranged that any "0" outputs are complemented by the inverters, while "1's are connected straight to the inputs of the 8-input NAND-gate.

Thus only when the correct key is inserted will all inputs to the NAND-gate be '1', so its output will go low. This triggers the monostable (½ 4528) producing an output pulse (1) which can be used to operate a solenoid bolt.

The Q output of this monostable also inhibits a second monostable. Depression of microswitch S1 by the key triggers the second monostable, whose output (2) is connected to an alarm circuit. Should an incorrect key inserted then the output of the 8-input NAND-gate will not go low and the first monostable will not be triggered.

### opticallock

santatronics

Thus the second monostable will not be reset by the Q output of the first, and the alarm will sound. The alarm may be reset manually by S2.

### Practical notes

The coding of the lock is set up using switches S3 to S10. Where a particular bit of the code is to be a '1' then the relevant switch is left in the position where the inverter is bypassed. Where a bit is to be '0' the switch is placed in the position where the output is taken from the inverter, thus complementing the bit and producing a '1' at the input of the 4068 8-input NAND gate. If one

ange the lock code

does not wish to change the lock code frequently then the switches may be replaced by hardwired links.

The number of possible codes for the lock depends upon the number of bits used. In the circuit given 8 bits were used for convenience of the IC package count (2 x 4011 and 1 x 4068 required) but there is no reason why the number of bits cannot be extended. Using 8 bits gives 28 - 2 or 254 possible combinations. The code 00000000 is not used as this corresponds to total illumination. which could be accomplished by an intruder depressing the microswitch with a piece of stiff wire or transparent plastic. Similarly 11111111 is not used, as in the event of lamp failure this code would be registered whatever key was

Finally, excellent phototransistors can be made from BC 108s by (carefully) sawing off the top of the can and filling with transparent casting resin as sold in handicraft shops.

### sixpence detector for

christmas pudding

This handy metal detector will greatly increase one's chances of obtaining a piece of Christmas pudding with a sixpence in it, or if one is really lucky, a silver threepenny bit (Daddy, daddy, what's a threepenny bit?).

The principle of operation is simple and well-known. It consists basically of two oscillators, one of which is a fixed frequency reference oscillator, and the other an oscillator whose frequency-

determining inductance is a search coil. Initially the two oscillators are adjusted so that their frequencies are nearly the same. The two outputs are fed into a mixer which will produce the sum and difference frequencies and the oscillators are adjusted so that the difference frequency (beat note) is in the audio band. If a metallic object is now brought near the search coil its inductance will vary, altering the oscillator frequency and hence the beat note.

The circuit is very simple and is designed around a CD4011 quad 2-input NAND gate. The reference oscillator uses an inverter (N1) as the maintaining amplifier and a 470 kHz ceramic filter as the frequency determining element foor stability.

The variable frequency oscillator (N3) uses an LC resonant circuit with the search coil (L1) as the inductor, This scan be a coil of about 70 turns of insulated wire and a diameter of approximately 50 mm (2"). The mixer is simply a NAND gate (N2), and the 4th NAND gate in the package (N4) is used as a buffer amplifier behind the variable frequency oscillator.

If a crystal earpiece is used, the transistor can be omitted – the output of N2 can drive the earpiece.

santatronics

# function generator generator ic 2206 Function generating ICs have been on the market for several years. Now one can refer to a 'second

Function generating ICs have been generation' of these ICs for technical progress has resulted in improved performance at only slightly higher prices.

A commonly used function generator IC is the type IC 8038 (ICL). This IC however has several 'blemishes', which severely limit its application. In particular the distortion factor of the sine signal the frequency range, the linearity and maximum frequency sweep of the VCOs are not satisfactory. The newer IC XR 2206 (Exar) offers, apart from substantially better performance, additional functions also. The advantages of the IC are summarised in table I, while table II lists the most important applications.

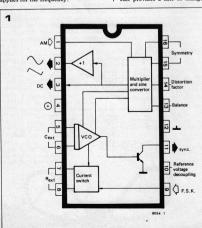

### Description of functions

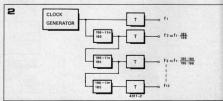

The IC contains four groups of functions as shown in figure 1, i.e. a voltage controlled oscillator (VCO), a function block 'switchable current sources', an analogue multiplier with sine convertor, and a buffer amplifier. The central unit of the function generator is the VCO. This is actually a current controlled oscillator (which by the way applies to most VCO circuits)! The frequency of the VCO is determined by a capacitor and a control current. Integrated current switches switch this current to one of the two current outputs (pin 7 or 8) of the IC, depending on the logic level of the selector input (pin 9). A linear relationship exists between the control current If, flowing from one of these outputs to earth, and the frequency of the VCO as follows:

$$f = \frac{I_f}{3C}$$

(Hz, A, F).

If the current is given in mA and the capacitance in  $\mu$ F, then:

$$f = \frac{330 \text{ If}}{C}$$

Current values between 1 µA and 3 mA are permissible for If, but optimum temperature stability will be achieved only in the range 15 to 750 µA. The current connection pins 7 and 8 are low resistance outputs, and the voltage at these points is stabilised to 3 V within the IC. As this reference voltage exhibits only a very small temperature coefficient (6 · 10-5 V/°C), the temperature stability of the oscillator frequency is also very good. It is practically only dependent on the temperature coefficients of the external components determining the frequency.

In the simplest case adjustment of the control current is effected by means of a resistance Rf between pins 7 or 8 and earth. In this case the control current is:

$$I_f = \frac{3 \text{ V}}{R_f}$$

and accordingly

$$f = \frac{I_f}{3C} = \frac{1}{R_f \cdot C}$$

applies for the frequency.

Permissible resistance values lie between 1 k and 2 M, and for good temperature stability between 4 k and 200 k. The capacitor which determines the frequency can be chosen between 1 nF and 100 uF. The most important properties of the integrated VCO can be seen in table III.

The VCO signal switches an integrated output transistor, the collector of which is accessible at the synchronisation output, pin 11. At this output a square pulse signal is available. In addition to this, the VCO signal provides the basis for the signal generation carried out in the multiplier and sine converter section. This part of the circuit provides a sine or triangular signal

#### Table I: Advantages

Low distortion factor, typically 0.5%.

High frequency stability, typically

3

- 2 10<sup>-5</sup>/°C.

\* Large relative frequency deviation,

- typically 2000 : 1.

- Low frequency dependance on supply voltage, typically 0.01%/V.

Linear amplitude modulation

- Wide supply voltage range, 10 to 26 V.

### Table II: Applications

Signal generation: sine, triangle, sawtooth, square.

Wobbulators.

AM/FM generators.

Frequency shift keying. PLL circuits.

Automatic measuring and testing equipment.

at the output, dependent on the external circuitry connected to pins 13 and 14. Provision exists for adjustment of curve shape (distortion factor), symmetry, amplitude and DC level of the output signal. If careful balance of curve shape and symmetry are carried out, the distortion factor of the sine signal is about 0.5%. This is adequate for most applications.

### Basic circuit for function generator

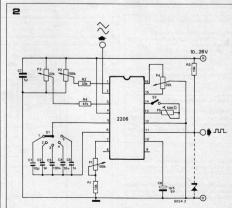

The basic circuit for a function generator incorporating the IC 2206 is shown in figure 2. With relatively few external components, the circuit generates sine.

### Table III: VCO specifications

Figure 1. Connections to the IC (top view).

Figure 2. A function generator.

Figure 3. Frequency plotted as a function of the value of P1.  $C_{\text{ext}}$  is 1  $\mu\text{F}$ .

triangular and square wave forms in five frequency ranges from 1 Hz to 100 kHz. Capacitors Cl to C5 select the frequency range. Cl should be a tantalum electrolytic capacitor if possible, Pl enables a frequency decade to be covered in each range, and for good frequency stability a value of 100 k was chosen. The relationship of frequency to Pl is shown in figure 3.

Because of the relationship  $f=1/R \cdot C$ , the frequency v. PI graph is not linear but hyperbolic. A more linear relationship may be obtained by the use of a logarithmic potentiometer. Capacitor C6 decouples the internal reference voltage source.

A square wave output is available at

pin 11 and resistor R2 provides a collector load for the internal output traisistor. For TTL compatibility the output amplitude must be limited to 4.7 V by the zener diside, shown connected by the broken line. Pin 2 provides a triangular waveform of good inearity (1% departure) if the switch is open, and a sine wave if the switch is closes,

For low distortion balancing of the curve shape is sessntial. For this purpose the symmetry potentiometer P4 is first unred to its central posttion and P5 is adjusted to give minimum distortion of the output signal. A further reduction of the distortion factor can then be achieved by readjustment of P4. If a distortion factor of about 2% is accept-

able, then this adjustment can be waived, P4 is then not required and P5 is replaced by a fixed resistor of 200  $\Omega$ . The potentiometer P2 is used for amplitude adjustment of the sine or triangular signal. The maximum output voltage is equal or greater than  $V_b/2$ . The output impedance at pin 2 is about 600  $\Omega$ .

The DC level at the signal output corresponds approximately to the DC voltage at pin 3 of the IC, and this is adjustable by P3. If the circuit application does not demand otherwise, then one should

adjust to  $V_b/2$ , in which case P3 can be replaced by a symmetrical potential divider  $(2 \times 12 \text{ k})$ .

The most important technical data of the circuit shown in figure 2 are summarised in table IV.

FM generator and wobbulator

As already mentioned in the functional description, the VCO frequency is proportional to a control current I<sub>f</sub>. By changing this current the frequency

can be varied over a wide range (max 2000:1), see table V. A possible form of current control would be the insertion of a controllable current source at outputs 7 or 8 of the IC. This solution turns out to be too complicated in practice and also leads to linearity problems.

A simpler proposal is shown in figure 4a. In this case the control current is changed by means of an opposing voltage applied to Rf. The difference between the voltage V<sub>0</sub> (3 V) and the control voltage V<sub>f</sub> is dropped across the

### Table IV: Specifications, figure 2

Square

Distortion factor, sine signal

Without balance

With balance

0.5% typical

1.5% max.

1.5% max.

Linearity, triangular signal

Amplitude stability (for frequency change

1000:1)

0.5 dB typical

### Table V: Specifications, figure 4

Max. relative frequency deviation 2000 : 1 typically (R<sub>f</sub> = 1 k to 2 M) Wobble linearity

10 : 1 Wobble amplitude

2% typically (f = 1 kHz to 10 kHz) 1000 : 1 Wobble amplitude 8% typically (f = 100 Hz to 100 kHz)

FM distortion (Amplitude ±10% of f<sub>o</sub>) 0.1% typically

### Table VI: Specifications, figure 6

Figure 4a. A wobble generator. The current  $I_f$ , which determines the frequency, is proportional to  $V_f$ .

Figure 4b. Adding resistor  $R_p$  to the circuit shown in figure 4a increases the current  $I_f$ , thereby shifting the frequency.

Figure 5. A generator for frequency shift

keying (FSK).

Figure 6. A sawtooth/impulse generator.

resistor. Thus the current  $I_f$  is proportional to the voltage  $V_f$ , and the frequency changes linearly with the voltage  $V_f$ .

Expressed in mathematical terms the relationship is as follows:

$$I_f = \frac{V_O - V_f}{R_f}$$

For the frequency:

$$f = \frac{I_f}{3.C}$$

and after substitution for If:

$$f = \frac{V_O - V_f}{3 \cdot C \cdot R_f} = \frac{3 \cdot V - V_f}{3 \cdot C \cdot R_f}$$

In this it is ESSENTIAL to note that the voltage V<sub>2</sub> under no circumstances exceeds the voltage V<sub>2</sub>, as the current flowing into the IC would lead to its destruction. If linearity is not essential, a diode can be added in series with the current output. The guide lines given in the functional description apply to the choice of the current I<sub>I</sub> and the resistance R<sub>I</sub> respectively.

A second wobbulator is shown in figure 4b. It differs from the first proposal only by the additional resistance  $R_p$ , through which the current  $V_0/R_p = I_{Rp}$  flows continuously, and which has to be added to the current  $I_{Rp}$ . Therefore:

$$I_f = I_{Rf} + I_{Rp}$$

applies for If.

The derivation for the frequency results

$$f = \frac{1}{R_p \cdot C} \cdot \left[ 1 + \frac{R_p}{R_f} \cdot (1 - \frac{V_f}{3}) \right] .$$

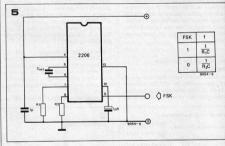

### Frequency shift keying (FSK)

The term frequency shift keying means the transmission of digital data (e.g. symbol transmission) by two fixed frequencies representing logic "0 and "1. This mode of operation is also possible with the IC 2206. As two interswitchable current outputs are available, two different frequency determining resistors can be inserted, thus producing two different fixed frequencies."

The change-over takes place by means of a digital input control (FSK input pin 9). The FSK input is TTL compatible. At voltages > 2 V or open circuit input, the control current flows via R1, and at voltages < 1 V it flows via R2. To make the relationships clear, a truth table is given in figure 5.

The circuitry associated with the signal processing section is analogous to figure 2 and depends on the required shape of the output signal.

### Amplitude modulation

The amplitude of the sine/triangular output changes linearly with the voltage at AM input pin 1 of the IC. This makes amplitude modulation of the signal possible. If the modulation voltage reaches the value V<sub>b</sub>/2, then a phase shift of the output signal takes place, and at the same time the amplitude passes through zero. Thus the IC is also suitable for

phase modulation and amplitude modulation with suppressed earrier. This latter permits, for example, the generation of a stereo multiplex signal. The AM dynamic range is 55 dB max, corresponding to a modulation index of almost 1 (m = 0.996). The AM input is of relatively high impedance, being at least 50 kB.

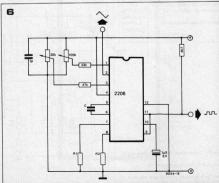

### Sawtooth and impulse generator

A link between the square output and the FSK input leads to an 'automatic' frequency shift keying. Two time constants differing from each other and determined by the resistors R1 and R2 control the positive and negative half cycles of the output signal. Pulse duration and duty cycle are adjustable between approx. Ve and 99% by means of R1 and R2. The following equations define frequency and duty cycles:

$$f = \frac{2}{C} \cdot (\frac{1}{R_1 + R_2}).$$

Duty Cycle:

$$\frac{R_1}{R_1 + R_2}$$

.

Table VI gives information about the 'quality' of the square output signal. The analogue output 2 gives an asymmetric triangular waveform (RI  $\neq$  R2), and at very low or high duty cycle (<10% or >90%) the waveform becomes a sawtooth

### Summary

The examples of application given are intended as a survey of the many possibilities resulting from the IC concept. Wherever there is a requirement for the production of signals of differing wave shape, at frequencies of up to several hundred kilohertz, it is worthwhile to consider whether the requirement could be met by the use of such an integrated component. This applies in particular to the hobby motivated electronic enthusiast because the combination of relatively complex circuit functions in one IC gives greater reliability to the complete circuit.

Literature: EXAR Data sheets and application reports.

### went sundruce-

Our offices will be closed on Wednesday, Thursday and Friday 24 - 26 December, and on Newyear's day.

The Monday afternoon technical queries service will not be available on Monday 29 December.

# coming

Front-end for TV sound — this will convert the existing design (Elektor no. 2, p. 236) into an entirely independent receiver for tv sound.

Automatic rhythm generators for the minidrum — add-on units that will give several complete rhythms at the flick of a switch.

TV tennis extensions — additions to the basic game (Elektor 7, p. 1111) giving new games, noises and scoring.

Audio preamplifier — a low-cost, high performance preamplifier and control amplifier with 'remote control' capability.

Digital wrist-watch — using only one IC.

Morse code units - a reader, writer and automatic call generator.

In most cases the current for a racing track is supplied by a mains voltage unit fitted with a three-position switch, with which the maximum voltage, and hence the maximum speed of the car can be adjusted. Although it is likely that in practice only the fastest position will be used, it is in view of the younger racers that the circuit is so designed that (by means of a potentiometer) it can be used with all positions of the switch on the supply unit.

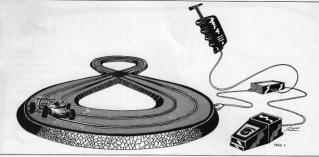

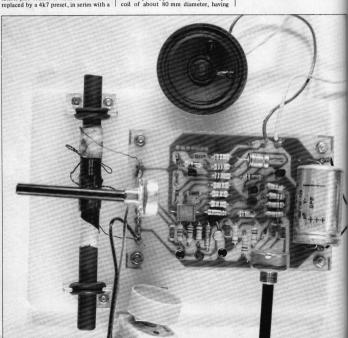

Actual 'acceleration' is done with an external potentiometer, for which the existing squeeze control can be used, although an ordinary 150 I carbon potentiometer will give better results. A handy tinkerer will undoubtedly find a way of also using an ordinary rotary potentiometer with the 'squeezer' Figure I shows what the circuit described here might look like in practice.

### The diagram

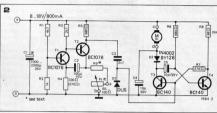

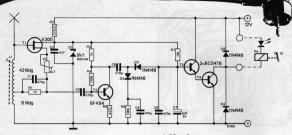

The design of the race-track control comprises a monostable multivibrator which is triggered by an astable multivibrator. The motor in the racing car is driven by the negative-going pulses of the monostable.

The width of these pulses is constant; the frequency (and hence the average voltage to the car motor) is governed by the setting of the astable. By means of the squeeze-potentiometer the frequency of the astable and indirectly the speed of the racing car is controlled. Figure 2 shows a circuit diagram.

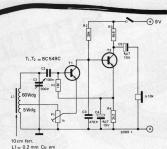

T1 and T2 are used in the astable. This astable is emitter-coupled, which does slightly decrease temperature stability, but has the advantage that only one canacitor (C2) is needed.

The frequency of the multivibrator can be adjusted by R9 and P1. Here potentiometer P1 represents the squeeze control.

The square wave produced by the astable is differentiated by capacitor C3 and the base-emitter junction of T3. The negative-going pulses are clipped by D1. The remaining positive pulses arrive at the base of T3 thus triggering the monostable consisting of T3 and T4.

The motor of the racing car is included in the collector circuit of T3 and is driven by the negative pulses of the monostable which have a constant width. This is how the 'engine' sound is obtained. The frequency of this pulse train and consequently the speed of the motor is determined by the speed of the astable which as already explained can be varied by means of R9 and P1. D2

and C4 are fitted to suppress any back

e.m.f. generated by the motor of the

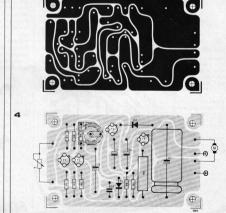

Figure 3 shows the board and figure 4 the component layout of the race-track control. If the case of the existing supply unit is sufficiently large, the complete circuit can probably be built in. Should this not be possible, a separate box can be used as illustrated in figure 1.

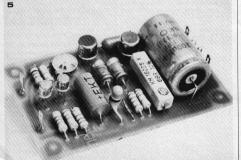

Figure 5 shows a photograph of a completed board.

#### Adjustment

racing car

The voltage supplied via the trafo may

Figure 1. The controller in use, connected between the mains power unit and the race track

Figure 2. The circuit diagram for race-track control. It is recommended to use a preset potentiometer for R9 (see text); P1 is the external squeeze control.

Figure 3. P.C. board for the race-track control,

Figure 4. Component layout of the board shown in figure 3.

Figure 5. A photograph of the board com-

range from 8 to 18 volts. The maximum current consumption may be 800 mA. If a three-position mains supply is available, the value of R9 must, of course, be adapted to the various voltages. In the 'slowest' position R9 must be about 47  $\Omega$ , in the centre position about 56  $\Omega$ , and in the 'fastest' position about 82 \Omega. It would be easy, of course, to use a  $100 \Omega$  adjustment potentiometer for R9; this possibility has been taken into account in the board layout. With the mains supply set in a particular position the best adjustment procedure is as follows: the squeeze control (P1) is first fully depressed and held in that position. Then R9 is so adjusted that the connected racing car runs at the maximum required speed, When the mains supply unit is set to another switch position, this adjustment must be repeated.

3

### Parts list

the

int

l is lse the the

ck

he

4

ck

Resistors: R1 = 4k7 R2 = 1 k R3 = 2k7

R4 = 330  $\Omega$  (270  $\Omega$ ) R5.R6 = 680  $\Omega$

R5,R6 = 680 12 R7 = 270 Ω

R8 = 68 Ω R9 = see text

P1 = existing 'squeezer' control 60-100  $\Omega$  (or potentiometer 150  $\Omega$ )

Capacitors: C1 = 1000-2200 µ/25 V

C2 =  $100 \mu/10 \text{ V}$ C3 = 2n7C4,C5 =  $10 \mu/25 \text{ V}$

Semiconductors: T1,T2 = BC107B T3,T4 = BC140

D1 = DUS D2 = 1N4002, BY126

### mini-MW

This receiver is so simple that very little outlay is required for its construction, and since only a small number of components are used it is ideal for miniaturisation, so that it will easily fit in a coat pocket. Nevertheless it gives good reception of local stations without the need for an external aerial or earth.

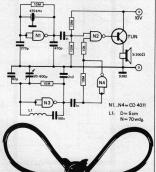

Operation of the receiver is exceedingly simple. Transistor T1 functions as an r.f. amplifier and detector with regenerative (positive) feedback. The degree of feedback, and hence the sensitivity of the receiver, can be controlled by P1. Although the output to the base of T1 is taken direct from the 'top' of the tuned circuit L1/C1, rather than via a coupling winding, the impedance presented by T1 is sufficient to ensure that

Detection takes place at the collector of T1 and the output impedance of this stage and C3 filter out the r.f. component of the rectified signal. T2 provides additional amplification of the a.f. signal to drive a crystal earpiece.

### Construction

A very compact p.c. board layout is shown for the receiver. L1 should be mounted as close as possible to the board to avoid instability problems. Those who wish to miniaturise the design still further can experiment by reducing the dimensions of the ferrite rod and increasing the number of turns to achieve the same inductance, though if L1 is made very small an external aerial may be necessary, which can be connected to the top end of L1 via a 4.7 p. capacitor.

4.7 p capacitor.

The recommended dimensions for L1 are 65 turns of 0.2 mm (36 S.W.G.) enamelled copper wire on a 10 mm diameter 100 mm long ferrite rod, with the tap 5 turns from the 'earthy' end of the coil.

CI can be a miniature (solid dielectric) 500 p variable capacitor, or for reception of a single station only it may be replaced by a fixed capacitor of just less than the required value in parallel with a 4-60 p trimmer. This will enable the size of the receiver to be further reduced.

Finally, the current consumption of the receiver is extremely low (approx. 1 mA) so that it will operate for several months on a PP3 battery.

santatronics

### Parts list

Resistors: R1 = 1 M

R2 = 39 k R3 = 6k8

R4 = 2k2 P1 = 1 k potentiometer

#### Capacitors: C1 = 500 p (variable) C2 = 100 n

C2 = 100 n C3 = 470 p C4.C5 = 4µ7/6 V

Miscellaneous: T1,T2 = BC 549C L1 = tuning coil (see text)

### R. ter Miitelen

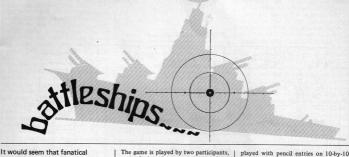

It would seem that transtical electronic engineers will apply their skills to just about anything — the means justifying the end. This article describes an electronic version of the well known game of 'battleships'. The pencil and paper have been replaced by switches and LED's — under the control of a boxful of TTL. The proposal, as it stands, should provide plenty of fun — as well as a challenge to exerpenced bartleshipsplayers to improve on the details!

The game is played by two participants, each of whom has a control panel. Each player also has a 10-by-10 cross-bar 'sea' in which he positions 10 ships by inserting jacks at the desired coordinates. The opponent can 'shell' any position by setting up a coordinate on switches before 'firing'. Any hit is displayed by LEDs. The players fire shells in turn, until one of them has lost all his ships.

### The original game

The original game of 'battleships' is

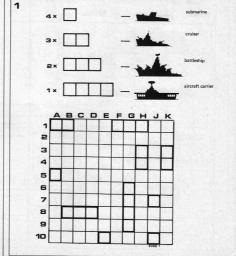

played with pencil entries on 10-by-10 sheets of square is identified by a coordinate-pair, such as A-1. The ships are positioned by out-lining the squares that they occupy. In one version of the game, each player has a 'fleet' consisting of: 4 submaries (one square each), 3 cruisers (two squares in-line) and an aircraftcarrier (4 squares in-line) and an aircraftcarrier (4 squares in-line) by the property of the control of

Figure 1. Example of a 'fleet' positioned in the 10-by-10 square 'sea'. Note that none of the ships touches any other, neither in vertical nor in horizontal direction.

figure 1). Neither player knows (for obvious reasons!) where his opponent has positioned ships.

Suppose now that player I opens up by announcing 'shell on A-I'. The answer is 'fuit'. (If the ship on A-I had been a submarine, player 2 would have had to answer 'hit and sunk'.) Player I now only knows that the ship is not a submarine - just what it is and how it is laid out he will have to determine during later turns.

during later turns. It is now player 2's turn to announce a coordinate and receive an answer. Player 1 has to guess the lie of the ship he has already hit. If he is lucky (or, at later stages of the game, clever enough), he will call 'shell on B-1' - and the answer will be 'hit and sunk'. He now knows that the ship was a cruiser and that there is no need to waste ammunition on the squares A-2, B-2, C-1 or C-2. The unoccupied-zone rule prevents his opponent from using them. The game continues shell-turn by shellturn until one player has lost his entire fleet, so that his opponent is the winner.

### The electronic game

As already mentioned the ship-positioning in the electronic form of the game is done by inserting jacks at the appropriate points on a 10-by-10 crossbar. There are several mechanical approaches to this. What in fact happens is that the paired inputs of the logic gates that represent shipping are plugged into the crossed busbars of the 'sea'. One input goes to one of the vertical busbars A to K (the letter I is omitted). the other input to one of the horizontal busbars 1 to 10. The sea area occupied by each player is scanned by the coordinate-switches on his opponent's playingdesk.

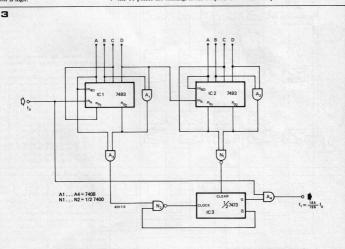

### The logic circuitry

Figure 2 gives the logic circuitry inside the left-hand playingdesk. Note that the 'sea area' drawn upper right is that mounted in the right-hand desk.

Suppose now that it is the left-hand player's turn, indicated by the glowing of LED 22 ('ready to fire'). The output of N3 is '0'. The player selects the square he wishes to shell by means of the coordinate switches (in the earlier example A and 1). When he presses the 'fire' button, any gate connected to the selected bushers will be pulled down to '0' via C2. The capacitor will prevent an unsporting player from sweeping his opponent's sea area by rotating the coordinate switches while holding down the 'fire' button.

when ss was pussion the riphit or to became "1. The release of this button causes NI output to go to "0", so the constant of the inputs S. The momentarity of the constant of

Figure 2. Circuit diagram of one half of the complete game, in this case the part that is installed mainly in the left-hand playing desk. The parts that inform the opponent of successful 'hits' and the 'ships sunk', the reset button and the 'sse' cross-bar on which he lays out his fleet, are installed (as given in the figure) in the right-hand playing desk.

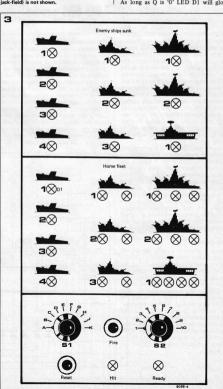

Figure 3. A possible layout for the controls and indicators on one playing desk, designed to provide a good survey of operations. The 'sea' cross-bar (that could for instance be a lack-field) is not shown.

In the example given above the shell on A-1 was a 'hit'. What happened in the circuit when the left-hand player pushed his firing button? It is convenient to trace the 'hit' in the circuit of submarine 1, to the upper left of figure 2. The two NOR gates N1 and N2 together form a set-reset flipflop. The reset input R is connected via S4 (push to reset) to the negative rail, so that it is at '0' level. If the output O of N1 is at '0', the flipflop will change state when a '1' arrives at the set-input S. This will occur whenever both inputs of N3 go to '0' - which is precisely what happens when these inputs are momentarily grounded via the sea-busbars and the opponent's coordinate switches and firing button. As long as Q is '0' LED D1 will glow

and LED D1R will be dark. D1 indicates the unsunk member of the home fleet -DIR would indicate to the opponent that he had sunk the submarine This indication is given when the flipflop N1/N2 changes state, causing D1R to glow and D1 to extinguish.

Each player clearly needs four of these circuits to represent his submarines. The other ships are represented by similar circuits, having one SR-flipflop for each square the ship occupies. When all the LED's associated with any ship have extinguished, the NAND gate that monitors the wellbeing of the ship concerned will indicate to the opponent that this target has been sunk. Only then does this player know what type of ship he has sunk; up to then he was only informed by a 'hit' indicator that illuminates for a few seconds after each successful push on the firing button. The 'hit' indicator consists of a SRflipflop, transistor T1 and LED 21. The input of N1 is normally at '1', because this input is connected via R2 to the positive rail. Whenever a '0' impulse arrives from a O output of one of the shipflops (sorry!) the SR-flipflop in the 'hit' indicator will switch, causing LED 21 to glow. The output of N1 will go to '1', so that C1 will charge through R5. After about 3 seconds this results in T1 starting to conduct, thereby pulling down the N2 input. This resets the flipflop, extinguishing LED 21 until the next hit is made. Each player has one 'hit' indicator, which is connected to the O outputs associated with the enemy ships.

Before a game can start it is necessary to reset all the shipflops. This is done by pressing the push-to-break button S4. To make it unattractive to a player to accidentally-on-purpose use the reset facility during the actual game, it is arranged that the left-hand player's fleet is reset from the right-hand playing desk (and vice-versa). A player who presses the reset button on his desk, during the game, puts himself at a great disadvantage - since he cancels the record of all his own successful hits.

### The display

Figure 3 shows a possible layout for either playing desk, intended to provide a good survey of operations during the game. The upper section indicates the damage done to the enemy fleet - which ships have been sunk. The drive to the 10 LED's in this section comes from the opponent's desk. Figure 3 shows the LED's D11, through D101, corresponding to D1R through D10R on the circuit diagram of the left-hand desk

The centre section provides full information on all hits placed on ships of the home fleet. A ship is sunk when all the LED's associated with its display are glowing.

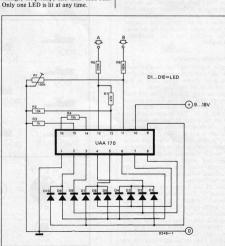

### **LED FM** scale

With home-made FM-tuners, the design and construction of the tuning scale often causes much brain racking, A mechanical solution is excluded from the very beginning because of the constructional difficulties. In many cases the only option left is a display of the tuning voltage (in the case of varicap tuners) by means of a voltmeter with its scale calibrated in frequency.

A Siemens IC type UAA 170, together with a few external components, provides an electronic scale. The table shows the relationship between tuning voltage, frequency, and LED read-out. The maximum available tuning voltage is connected to input A. This voltage must be kept constant as a reference voltage. The variable tuning voltage is fed to input B as control voltage. The

resistance ratios  $\frac{R6}{R7}$  and  $\frac{R7}{R2}$  determine the voltage difference required for each step of the LED display. The circuit values are chosen such that the voltage difference corresponds to a frequency change of 2 MHz.

The preset potentiometer R1 is used for scale adjustment. While R1 is being adjusted, the tuning voltage must be checked with a voltmeter. The adjustment is correct if the corresponding LEDs light up at the voltages given in the table

|                   | T               |     |

|-------------------|-----------------|-----|

| Tuning<br>Voltage | Tuning<br>Range | LED |

| < 4               | < 88            | D1  |

| 4                 | 88              | D2  |

| 5                 | 90              | D3  |

| 6                 | 92              | D4  |

| 7                 | 94              | D5  |

| 8                 | 96              | D6  |

| 10                | 98              | D7  |

| 12                | 100             | D8  |

| 15                | 102             | D9  |

| 18                | 104             | D10 |

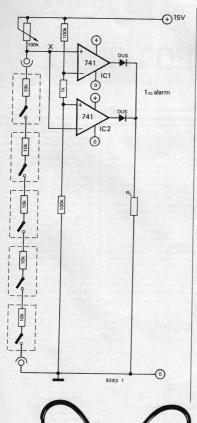

## alarm